芯片的工艺角

芯片的工艺角

芯片领域中的工艺角:概念与原理

在芯片设计中,“工艺角”(Process Corner)通常指的是制造过程中由于工艺参数的离散性(例如阈值电压、栅极氧化层厚度、掺杂浓度等)而造成的晶体管性能差异。不同的工艺角会导致芯片在速度、功耗等方面出现差异。为了保证芯片在各种可能的制造偏差条件下都能正常工作,设计工程师会在仿真阶段对不同工艺角进行分析和验证。

1. 什么是工艺角?

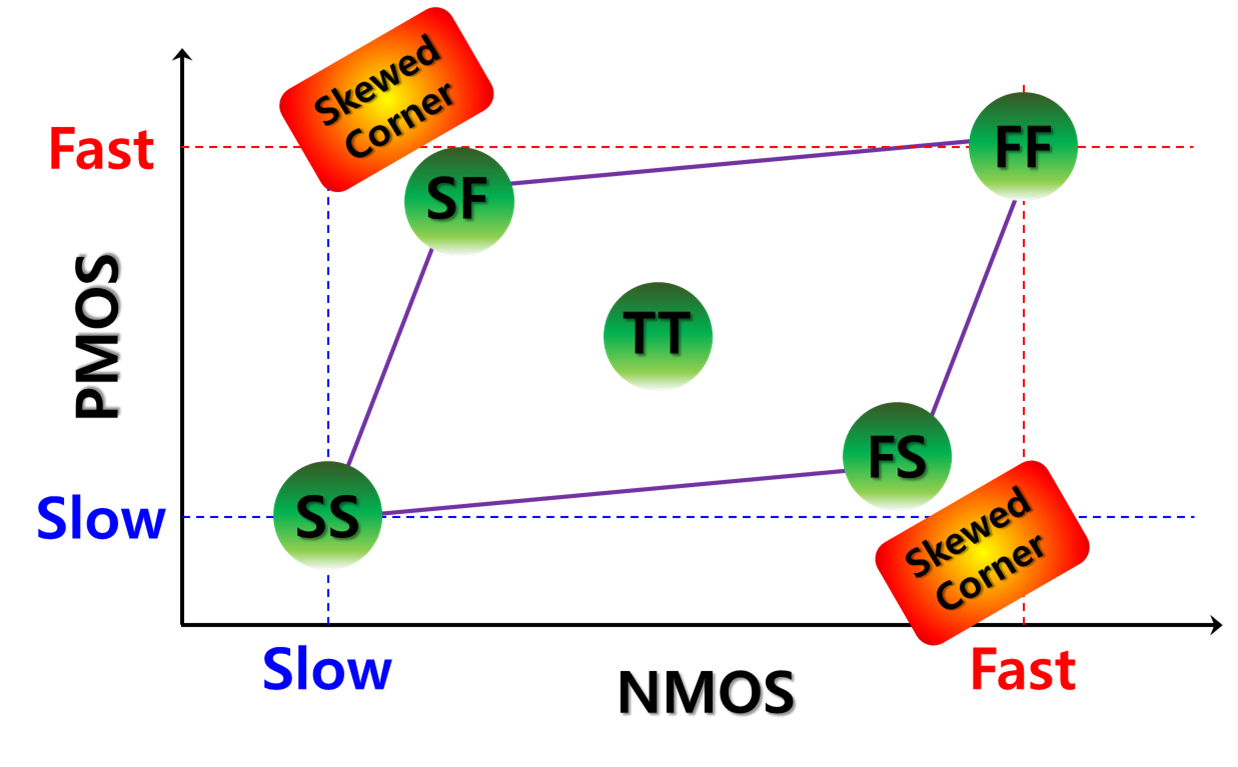

工艺角(Process Corner)可以理解为在晶圆制造工艺允许的范围内,器件性能的最坏或最好情况的组合。通常用几个关键词来描述:

- SS(Slow-Slow):NMOS 和 PMOS 都是“最慢”工艺角。

- FF(Fast-Fast):NMOS 和 PMOS 都是“最快”工艺角。

- TT(Typical-Typical):NMOS 和 PMOS 都是“典型”工艺角。

- SF(Slow-Fast):NMOS 慢、PMOS 快。

- FS(Fast-Slow):NMOS 快、PMOS 慢。

这里的“慢”和“快”并不是指实际的时钟速度,而是指器件的特性:阈值电压较高时,器件会偏慢;阈值电压较低时,器件会偏快。

2. 为什么要考虑工艺角?

半导体制造过程中不可避免地会有一定的工艺波动(Process Variation)。如果只针对“典型”工艺角进行设计和验证,那么在实际制造时可能会遇到比典型情况更差或更好的器件性能,从而造成电路无法正常工作、功耗或速度不达标等问题。

- 在慢角(SS)下:器件速度变慢,电路延迟增加;同时器件阈值电压通常更高,漏电流更小,静态功耗会有所降低,但动态功耗也会因为速度减慢而有不同表现。

- 在快角(FF)下:器件速度加快,电路延迟降低;但阈值电压通常更低,漏电流更大,可能导致静态功耗上升。

因此,设计工程师需要在快角、慢角等极端情况下进行时序和功耗分析,以确保芯片在这些最坏或最好条件下依然能够正常工作。

其他影响芯片性能的因素:电压与温度

除了工艺本身的差异外,芯片在不同电压和温度下的性能也会发生变化。为了全面反映芯片的工作范围,工程师通常会考虑PVT(Process、Voltage、Temperature)三个因素的组合,也称为PVT Corners。

- 电压(Voltage):工作电压的上限和下限会影响晶体管的驱动能力和漏电流。

- 温度(Temperature):高温会增加漏电流、减小迁移率,导致器件速度下降;低温则可能使器件速度上升。

因此,芯片设计通常要在最坏和最好的电压、温度条件下进行时序和功耗分析,确保芯片能够在整个 PVT 范围内可靠工作。

工艺角可能造成的影响

对 PIN 信号的影响

不同工艺角会影响 信号完整性、时序、功耗和驱动能力,对 输入(Input) 和 输出(Output) PIN 均有影响。

(1) 数字信号 PIN

影响因素:

传播延迟(Propagation Delay)

- FF 工艺角:MOSFET 开关速度快,延迟最短,可能导致时序收敛困难,甚至产生 赛道竞争(Race Condition) 问题。

- SS 工艺角:MOSFET 速度慢,延迟最长,可能导致 Setup 时间(Tsetup)或 Hold 时间(Thold)违例,影响时序可靠性。

上升/下降时间(Rise/Fall Time)

- FF 工艺角时,边沿更陡,可能导致高频噪声更强。

- SS 工艺角时,边沿变缓,可能影响高速通信接口,如 DDR、PCIe 等。

电平阈值(Logic Threshold)

- 不同工艺角会导致输入信号的高低电平阈值变化,影响输入信号的识别可靠性。

(2) 模拟信号 PIN

影响因素:

增益与失真(Gain & Distortion)

- FF 工艺角:MOSFET 的跨导(gm)更大,增益可能变高,但非线性失真也可能增大。

- SS 工艺角:跨导变小,增益可能下降,影响放大器性能。

输入偏置电流(Input Bias Current)

- FF 工艺角:漏电流增加,输入偏置电流可能增大,影响高阻抗模拟电路(如 ADC、运放)。

- SS 工艺角:偏置电流较小,但可能增加噪声。

带宽和相位裕量

- FF 工艺角:MOSFET 速度快,带宽可能增加,但相位裕量可能降低,导致不稳定。

- SS 工艺角:带宽下降,信号可能变得更慢,影响 ADC 采样率。

对干扰(EMI/噪声)的影响

工艺角会影响 电磁干扰(EMI)、串扰(Crosstalk)和电源噪声(Power Noise),进而影响 PIN 信号的稳定性。

(1) 电磁干扰(EMI)

FF 工艺角:

- MOSFET 速度快,信号切换更陡峭,高频分量更强,容易产生更强的 EMI。

- 需要额外考虑 PCB 走线屏蔽、地弹噪声(Ground Bounce) 及 去耦电容(Decoupling Cap) 的优化。

SS 工艺角:

- 由于信号上升/下降时间变慢,EMI 相对较弱,但会导致信号质量下降,如眼图(Eye Diagram)收缩。

(2) 串扰(Crosstalk)

FF 工艺角:

- 信号上升时间短,高频分量增加,容易导致相邻信号线(特别是高速总线,如 DDR)之间的串扰增强。

- 需要增加 信号屏蔽、差分走线 或调整 PCB 布局。

SS 工艺角:

- 信号传播时间变长,串扰相对较弱,但过慢的信号可能影响数据传输速率。

(3) 电源噪声(Power Noise)

FF 工艺角:

- 由于开关速度快,电流突变更剧烈,容易引起 电源纹波(Power Ripple) 和 地弹噪声(Ground Bounce),导致信号抖动(Jitter)。

- 需要优化电源去耦和 LDO/电感的设计。

SS 工艺角:

- 电流变化较小,电源噪声较低,但电路性能可能不足,如振荡器频率下降、PLL 锁定时间变长。

典型案例

| 应用 | FF 影响 | SS 影响 |

|---|---|---|

| 高速数字接口(DDR, PCIe, USB) | EMI 增加,可能出现信号反射 | 速度变慢,数据吞吐量下降 |

| ADC/DAC | 增益偏移,噪声增大 | 带宽变小,响应速度下降 |

| PLL(锁相环) | 锁定时间缩短,但相位噪声增加 | 锁定时间变长,可能无法正常工作 |

| 电源管理(LDO, DC-DC) | 纹波增大,可能需要更大的去耦电容 | 稳压变慢,响应滞后 |

设计优化策略

(1) 数字电路优化

- 采用 静态时序分析(STA),确保在 SS 工艺角 仍满足时序要求。

- 在 FF 角测试 EMI,如果过大,可调整信号上升时间(如插入小电容)。

- 适当调整 驱动强度,减少串扰影响。

(2) 模拟电路优化

- 在 SS 工艺角 下确保带宽足够,避免增益衰减影响信号质量。

- 在 FF 工艺角 下关注功耗和失真,避免 MOSFET 过驱动。

(3) 电源优化

- 采用 更好的去耦电容(如 X7R/X5R 陶瓷电容),减少电源噪声。

- 在 PLL 设计中,优化 环路滤波器(Loop Filter) 以适应不同工艺角。

- 适当增加 电源裕量(Voltage Margining),确保不同工艺角下都能稳定工作。

总结

工艺角(TT、SS、FF)不仅影响芯片的核心逻辑,还会对 PIN 信号质量、EMI、串扰、电源噪声 等方面产生显著影响:

- FF 工艺角:信号快、噪声大、功耗高、串扰强,时序更紧张。

- SS 工艺角:信号慢、功耗低、噪声小,但可能影响电路性能。

- SF/FS 工艺角:主要影响模拟电路的 P/N 不匹配问题,如放大器失调。

在设计时,需要 PVT(Process-Voltage-Temperature)联合仿真,并针对不同工艺角进行 时序分析、信号完整性优化、去耦设计,确保系统可靠运行。

在半导体工艺不断缩进(如从 7nm 向 5nm、3nm 演进)的过程中,器件的工艺波动日益显著,对设计的精细化管理也提出了更高要求。只有深入理解并有效应对工艺角的挑战,才能在芯片设计中保证高良率、高性能和低功耗,为最终产品提供可靠的技术支撑。