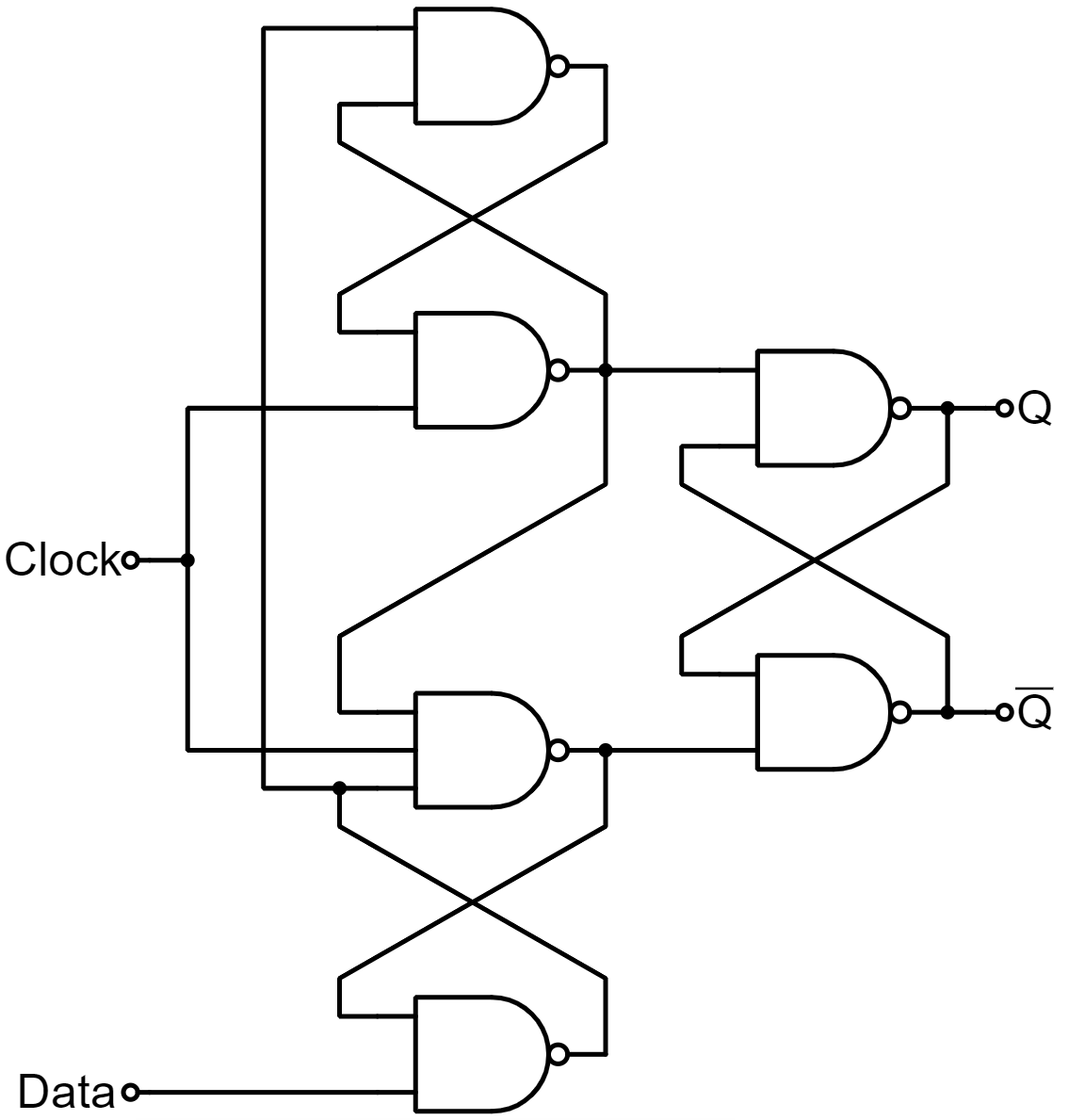

AXI4与AXI3的区别

AXI3和AXI4区别-思维导图

Brust support

AX4对burst length进行了扩展:

AXI3最大burst length是16 beats;AxLEN位宽是4bit

AXI4支持最大到256 beats,AxLEN位宽是8bit;但是这也是有限制的:

- 只有INCR burst type支持超过16 beats的Burst;WRAP and FIXED burst types 最大还是支持16 beats的Burst,和AXI3保持一致;

- Exclusive accesses 的burst length 必须小于 16.

在实际使用中,很少使用支持超过Burst Length超过16的命令,因为Burst Length太长会一直占用总线,影响了系统性能;而且AXI总线的一个限制就是Burst一旦开始是不能取消的,如果Burst太长,一旦出错,影响比较大。

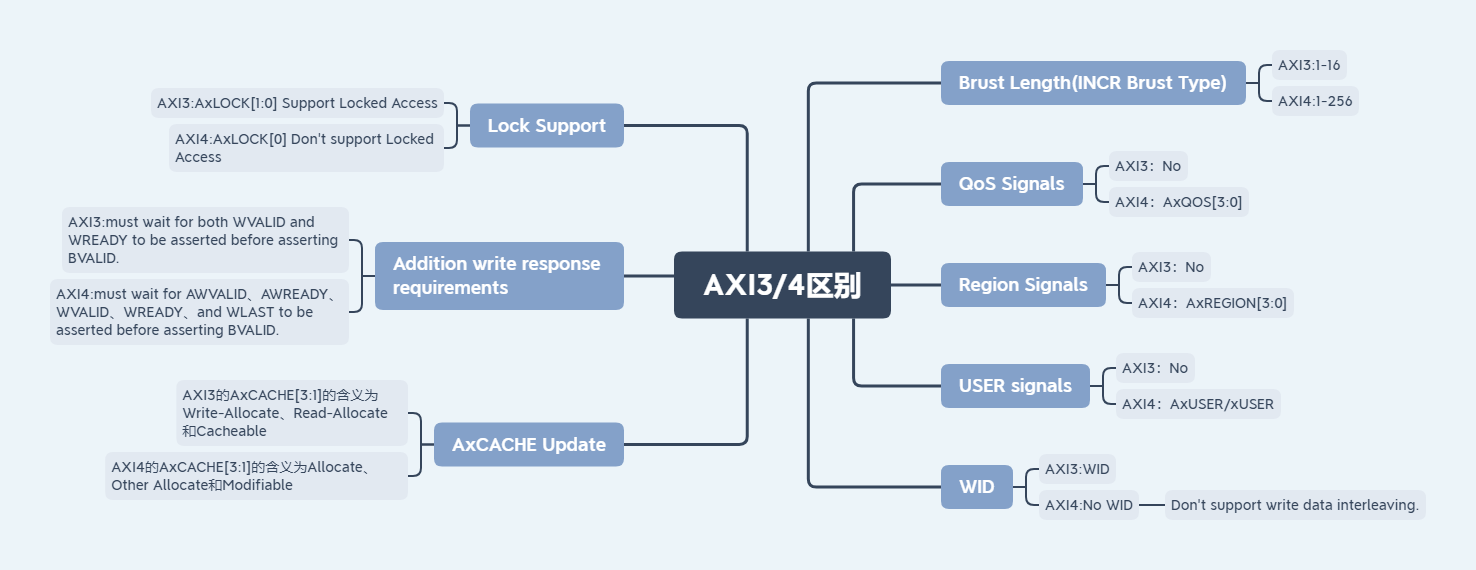

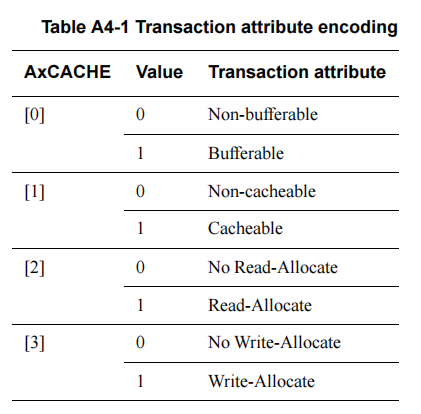

AxCACHE Update

AXI3中AxCACHE的含义

AXI4中AxCACHE的含义

含义可参考深入AXI4总线

Modifiable

- 单个传输事务可以被分解为多个传输事务

- 同理,多个传输事务也可被聚合为一个

- 读传输事务中,可以预取相邻地址上的读数据,要求目的地址返回比主机需求更多的数据

- 写传输事务中,可以访问比需求地址跨度更大的区域,其中使用 WSTRB 信号防止更新不相关的数据

cache-allocate

allocate

当前地址的数据可能因为前期的访问,已经分派空间并缓存于 cache 中

other allocate

当前地址的数据可缓存于 cache 中,是因为其他主机事务而分派空间缓存,或者是本机其他类型的事务而缓存。(对于读事务来说,就是先前的写事务,反之亦然)

- 当AxCACHE的高两bit为2‘b00时,表示CPU指示该传输事务无需至CACHE中查找,必须直接从主存储中读取或写入主存储;

- 当AxCACHE的高两bit为2’b11时,表示该传输事务必须首先在CACHE中查找,缺失的情况下再访问主存储。

Bufferable

表示该传输事务在传输至目的地的途中,可以被 interconnect 或者任意的 AXI 组件缓存,延迟若干个周期。一般应用于写传输事务。

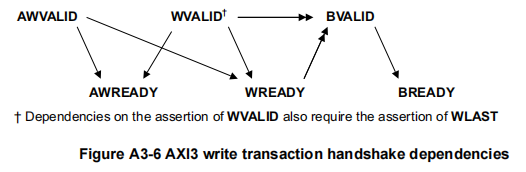

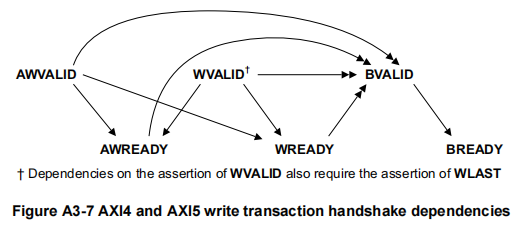

Addition write response requirements

AXI3:must wait for both WVALID and WREADY to be asserted before asserting BVALID.

AXI4:must wait for AWVALID、AWREADY、WVALID、WREADY、and WLAST to be asserted before asserting BVALID.

AXI3对BVALID的规定其实是有漏洞的,可能Transaction还未真正完成就发送了写响应。AXI4的更新更加合理和严谨。

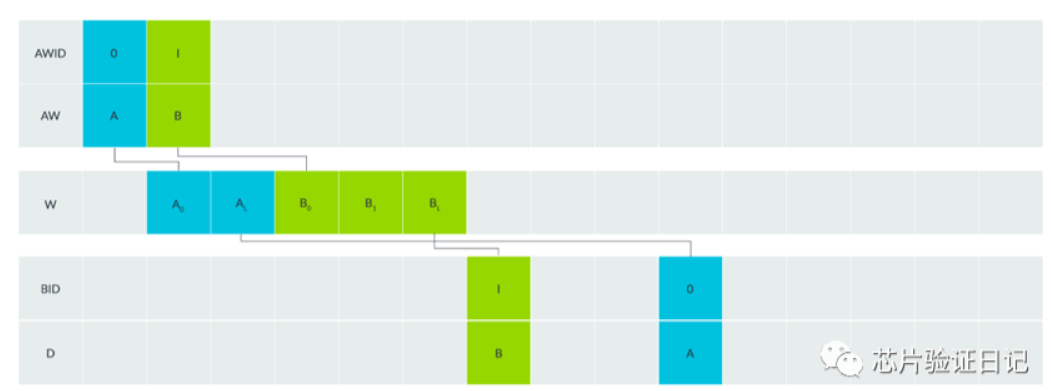

Write interleaving

AXI4协议去掉了WID信号,因此不支持写交错。这是AXI4和AXI3一个很重要的改变。

写交错的去除使得在WID信号上传递的信息是多余的。因为所有写入数据必须与相关的写入地址顺序相同,任何需要WID信息的部件都可以从写地址通道的AWID中获得这些信息。

写交错即指在AWID=0的数据还未发送完后,允许AWID=1的数据先发送;这样带来的代价是发送端必须要缓存多个ID的wdata,不管是master还是总线interconnect都必须要增加大量的缓存,所以增加了面积。

此外,写交错增加了系统总线设计的复杂度,且容易造成死锁。所以AXI4就把写交错功能去掉了。

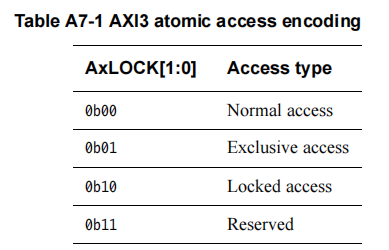

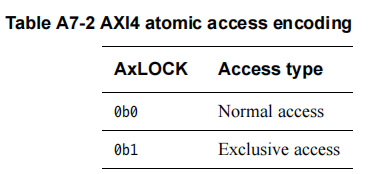

Locked transactions

AXI4去掉了对locked transaction的支持,对信号的影响就是AxLOCK从AXI3的2-bits减少到了1bit

为什么去掉Locked Access呢?按手册的说法(A7.3),有如下原因

- 大部分组件用不到这个功能

- 有Locked Access的话会增加互联(interconnect)的复杂性

Locked Access和Exclusive access有哪些区别呢?其实最主要的区别是作用的对象不同。

Locked Access作用的对象为总线,一旦发生Locked Access,那么其它的master都不能通过总线对该Slave进行访问。在一个复杂的SOC系统中,Locked Access对系统的影响太大了。万一发出Locked Access的master出问题,那么系统就会挂死。这种牺牲整个系统来成就某个master的机制当然最后会被淘汰。

Exclusive Access作用的对象为对应的Slave,支持Exclusive Access的Slave会实现一个monitor,记录发起Exclusive Access的master的ID,并记录后续发起写过程的master的ID号,进行对比。Exclusive Access对总线系统是没有要求的,只是对slave做了特殊要求。即使出错也不会影响系统的其它部分,最多是Exclusive Access失败而已。

Quality of service signaling

AXI4增加了2个4bit的QoS命令信号AWQoS、ARQoS。但是AXI4协议没有规定QoS的用法,因为这是一个需要全面考虑的特性。AXI4建议的QoS是AxQoS值越大,优先级越高。

增加QoS信号是随着越来越多的master对总线需求的冲突越来越明显,系统的带宽没有显著提升。那么如何给不同的IP分配不同QoS就是架构师需要考虑的事情,且没有不变的规律可以遵守。

Region Signals

AXI4为了支持区域标识,增加了AxREGION信号。区域标识符的使用意味着slave不必支持不同逻辑接口之间的地址解码。一般情况下使用地址的高位来区分不同的区域,而采用了区域标识符就不用采用地址解码区分了。另外,通过划分region,对某些physical allocation进行保护,比如某个region能被读写,而某个region只提供读权限。

这是一个可选的功能,ARM自己的CPU都很少支持。

USER signals

AMBA4中未对USER信号做任何规定,只是建议不要使用这个信号,防止IP直接互联不兼容。一般的IP厂商都不会使用,防止兼容性问题。

AXI3和AXI4的互联

我们分下面两种情况讨论

AXI4 master连接到AXI3 slave

- 因为AXI4没有WID信号,而AXI3有。但我们还不能直接把AXI4 Master的AWID直连到AXI3 slave的WID上,因为如果AXI4 master能发出outstanding的命令,当前的AWID的值和WID的值就不是对应的关系。通常的做法是将AWID缓存到一个FIFO钟,等到传完数据(收到了WLAST)再切换到下一个AWID,把这样读出的AWID当做WID使用。

- AXI3的AxLOCK信号是2bit的,直接将AXI3的AxLOCK信号的最低位连接到master上即可

- AXI4 master不能产生超过16beat的brust,因为AXI3不支持。

- 系统总线要么统一用AXI3,要么统一用AXI4。

- AXI3 slave必须注意BVALID的生成要符合AXI4协议,需要修改逻辑。

- QoS、USER、REGION等多余的信号需做额外的处理,一般赋默认值。

AXI3 master连接到AXI4 slave

- 由于AXI4是没有WID信号的,所以直接把WID浮空就行;

- AXI4 Slave的AxLOCK[0]连接到AXI3 master的AxLOCK即可;

- AXI4 Slave的AxLEN[7:4]=4’h0 即可;

- 系统总线要么统一用AXI3, 要么统一用AXI4;

- QOS/USER/REGION信号等多余的信号需要做额外的处理;

- AXI3 master必须不能支持Write interleaving,否则必须修改AXI3 master的逻辑。

AXI接口部分名词解释

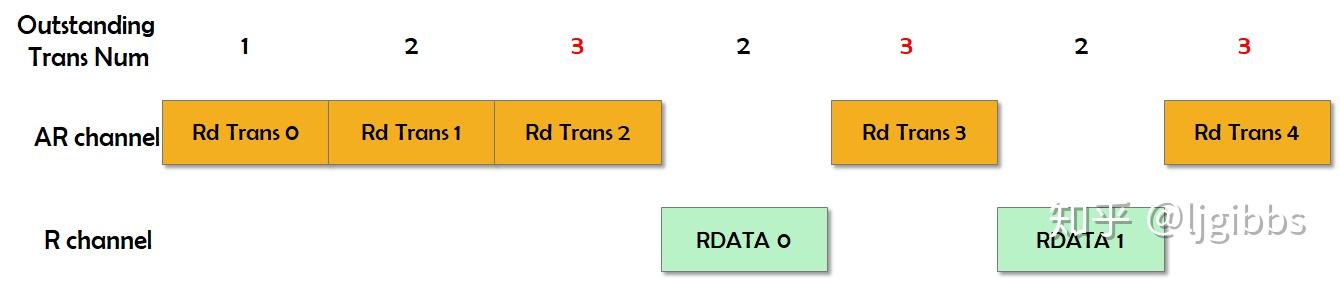

outstanding

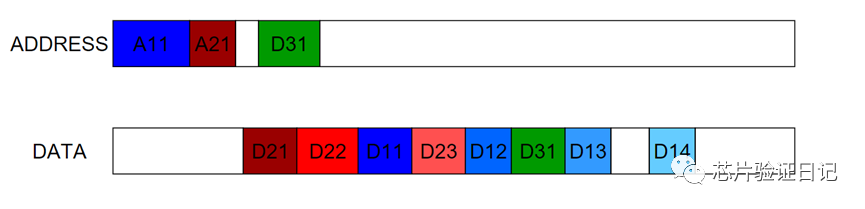

interleaving

AXI3中有,AXI4中被删除。

out-of-order

AXI Full vs AXI Lite

AXI Lite是AXI Full协议的简化版,主要区别在以下几点

- 突发长度固定为1;

- 数据通路要将数据位宽用满(不支持narrow transfer),还可以使用WSTRB信号,数据位宽可选32或64;

- 所有的访问都是Non-modifiable、Non-bufferable;

- 不支持Exclusive access;