DC入门

前言

Design Compile是所有IC工程师的必备工具,之前在校期间受限于平台只是使用FPGA的开发平台Vivado完成综合流程。进入公司后发现DC比较陌生,最近啃了一下Design Compile的User Guide,特用博客做记录用。开发环境为Design Compiler 2016。

综合概述

之前跟FPGA打过交道的同学应该对综合这个概念不陌生,FPGA里的综合是将HDL映射到FPGA的固有器件上,如LUT,BRAM,DSP等。而芯片中的综合也是类似,只不过底层被映射的器件变了。Design Compiler(以下简称DC)是Synopsys公司用于做电路综合的核心工具,可以将HDL转换为基于工艺库的门级网表。

DC工具中的综合主要分为以下三个阶段:

Translation(转译):把电路转换为EDA内部数据库GTECH(Generic Technology),这个数据库跟工艺库是独立无关的;

- analyze(分析):对HDL进行语法检查;

- elaborate(细化):将HDL转换为GTECH;

- Optimozation(优化):根据工作频率、面积、功耗来对电路优化,来推断出满足设计指标要求的门级网表;

- Mapping(映射):将门级网表映射到晶圆厂给定的工艺库上,最终形成该工艺库对应的门级网表。

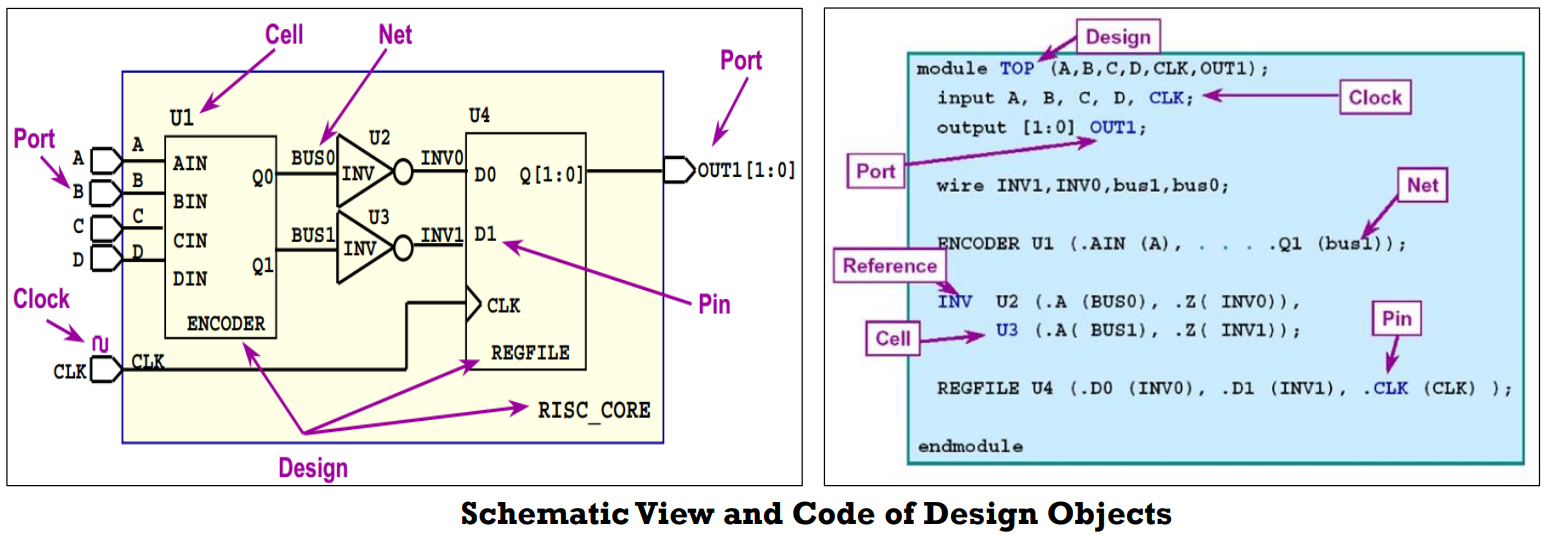

DC在综合过程中会将电路划分为下列的处理对象:

- Design:待综合的对象;

- Port:Design最外部的端口;

- Clock:时钟;

- Cell:被例化的模块名;

Reference:例化的原电路;

举例说明:

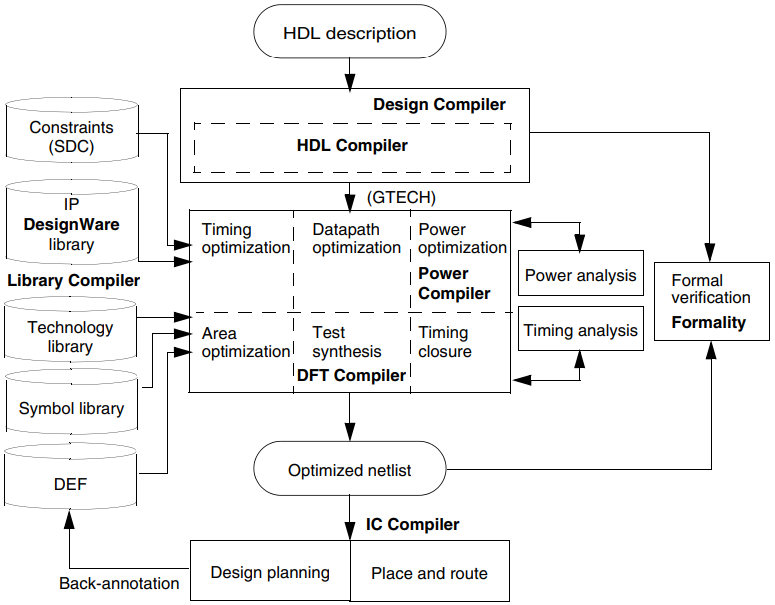

使用DC综合的流程如下图所示:

我们对着上图进行说明。HDL文件不用多说,硬件设计的主要文件;首先经过Design Compiler将HDL转换为GTECH,完成了Translation,然后进行后续优化与映射工作;

图中左侧有5个输入的“参考”文件。Constraints为设计约束文件,为sdc(Synopsys Design Constraint)文件,对设计进行面积,时钟等方面的约束;IP Designware Library为Synopsys设计的高性能算子库,对“+ - × >= <”等基础算子或其他高级的算术运算进行深度优化,并可根据设计目标选择面积优先或者速度优先的实现方式,但需要购买额外的License才可以使用;Technology Library为工艺库,又称Target Library,由Vendor提供,内部包含一些基本的电路模块,如与或非门,FF,Latch等,供HDL进行映射;Symbol Library为符号库,它定义了在GUI界面中综合后的电路如何显示,在需要查看和分析电路图时需要指定,不指定时默认都按方框显示电路模块;DEF(Design Exchange Format)文件是一种标准的电子设计交换格式,主要用于表示物理设计和布局信息。在进行FloorPlan与Place&Route后,对布局布线,版图信息等进行反标,提供给DC,用以更准确地对Timing,Area等进行评估与优化。

图的右侧是对Design进行时序和功耗的分析,中间则是优化的主要过程,如Timing, Datapath, Power, Area Optimization,进行时序收敛并对DFT(Design For Test)进行综合,最终得到优化后的netlist。

由于优化过程中的一些优化手段会改变原先的电路结构,因此在综合后需要对netlist与HDL进行一致性验证,也就是最右侧的Formal Verification(使用Formality工具)。最后我们将优化后的netlist提供给IC Compiler,完成Floorplan以及P&R等工作。

Design Compile的使用

启动Design Compile

一般使用命令行的方式来启动DC,启动方式为dc_shell -f script.tcl。DC在启动时会自动在启动目录下创建“command.log”和“view_command.log”两个文件,用于记录用户在使用DC时所执行的命令及设置的参数。

Translation

首先DC需要读取HDL文件,有如下两种读取方式:

- 使用read_file命令来读取文件;

- 同时使用analyze和elaborate指令;

read_file命令可以同时完成两件事:1. analyze the design;2. translate the design into GTECH;

那它与(analyze+elaborate)有什么不同呢?

| 比较 | read_file | analyze+elaborate |

|---|---|---|

| 输入文件类型 | 所有文件类型都支持,包括Verilog,VHDL,db文件等 | 仅支持Verilog和VHDL |

| 使用时机 | 用来对综合的网表,预编译的结果及代码等进行综合 | 对VHDL和Verilog代码进行综合 |

| 参数 | 不允许在命令中对参数进行修改 | 可以通过elaborate修改设计中的Parameter |

| Link Design | 必须使用link命令来解析模块引用 | elaborate自动执行了link命令来解析模块引用,无需再执行link |

link中使用elaborate命令来重新对parameter进行赋值的示例:

1 | elaborate chip_top -parameter "DATA_WIDTH = 8,ADDR_WIDTH = 8" |

Link

读取完所要综合的模块之后,需要用link命令将读到DC暂存区中的模块或实体连接起来。在tcl文件中需要添加link_library,告诉DC到哪去找这些模块。同时还要注意search_path中的路径是否指向该模块或单元电路所在的目录。

Tips:设置search_path后,DC会在search_path目录中自动查找指定的设计和库文件,无需指定其绝对路径,仅需指定其名字即可。search_path的作用范围不仅限于库文件,我们还可以将sdc,db等文件的路径放在其中,简化tcl文件的规模。

标准工艺单元库

DC需要工艺库文件来执行综合过程。工艺库文件是针对特定制造工艺的库文件,其中包含了对工艺的物理特性和约束信息进行建模。这些工艺库文件在综合过程中发挥着重要作用:

基本元件库: 工艺库文件包括了各种基本元件(如标准单元、存储器单元、I/O单元等)的信息。这些元件是IC设计中的基本构建块,它们的特性和电气特性必须准确建模以便综合工具能够正确地生成电路。

时序和电气特性模型: 工艺库文件中包含了不同元件的时序特性和电气特性的模型,例如延迟、功耗、面积、电压等。这些模型允许综合工具在生成电路时考虑这些关键性能参数。

约束信息: 工艺库文件包括与制造工艺相关的约束信息,如晶体管尺寸、金属层规则、布线资源、最小间距、最小尺寸等。这些约束信息确保生成的电路在特定工艺下能够正确制造。

优化和分析: 工艺库文件中的信息用于进行优化和分析。综合工具使用工艺库中的特性来选择最佳电路结构,以满足性能、功耗和面积等要求。

工艺相关的约束: 工艺库文件还包含了与工艺相关的约束,如抖动、噪声、温度等。这些约束信息在特殊情况下,如高性能或低功耗设计时,起到关键作用。

制造可行性: 工艺库文件确保综合工具生成的电路在实际工艺下是可制造的。这包括考虑工艺的限制,以避免制造上的问题。

DC使用工艺库文件来将逻辑网表转化为物理电路,确保生成的电路在特定工艺下满足性能、功耗和面积等方面的要求。因此,工艺库文件是IC设计工具中至关重要的一部分,它们在整个设计流程中起着关键的作用。

常见库文件

- 目标库(target_library):主要包含电路的标准单元;

- 链接库(link_library):包含付费IP、存储器、IO、PAD;

- 符号库(symbol_library):定义了在GUI界面中综合后的电路如何显示;

- 算术运算库(synthetic_library):对基本的算子进行映射,即Design Ware library;

目标库

目标库是综合后电路网表要最终映射到的库。

读入的HDL代码首先由Synopsys自带的GTECH库转成DC内部交换的格式,然后经过映射到目标库,最后生成优化的门级网表。

目标库一般是db格式,由lib格式转化而来。

目标库包含了各个门级单元的行为、引脚、面积、时序信息等,有的还包含了功耗方面的参数。

DC在综合时就是根据目标库中给出的信息来计算路径的延时,并根据各个单元的延时、面积和驱动能力的不同选择合适的单元来优化电路。

链接库

链接库是设置模块或单元电路的引用。

对于所有DC可能用到的库,我们都需要在link_library中指定,也包括要用到的IP。

在link_library的设置中必须包含“*”,表示DC在引用实例化模块或者单元电路时首先搜索已经调进DC的模块和单元电路。

符号库

符号库是定义了单元电路显示的原理图库,查看分析电路图时,需要设置sdb格式的符号库。

算术运算库

在初始化DC时,不需要设置标准的DesignWare库standard.sldb用于实现verilog描述的运算符,DC会把加法、乘法等运算综合成性能较差的电路。

如果需要扩展DesignWare,需要在synthetic_library中设置,同时需要在link_library中设置相应的库以使得在链接的时候DC可以搜索到相应运算符的实现。(注意:DesignWare需要更高级的licence)

DC约束

DRC约束

DRC(Design Rule Check)用于确保生成的电路与制造工艺的物理规则和限制相符,在综合过程中的主要作用是确保所生成的电路在制造时不会违反工艺规则,从而提高设计的可制造性,减少错误,确保电路性能和功耗在预期范围内,并支持工艺迁移。这些约束对于确保IC设计的成功和高质量至关重要。

常见的DRC约束有以下三种:

- set_max_transition:约束design中的信号、端口、net最大transition不能超过这个值,值越小越苛刻;net的transition time取决于net的负载(fanout),负载越大,transition time越大;

- set_max_fanout:对design、net、output port进行操作,该约束用于限制一个逻辑门(或一个寄存器)的输出信号驱动的负载数量。它规定了一个逻辑门的输出可以连接到多少个输入;(Max fanout load of net is max number of loads the net can drive. )

- set_max_capacitance:该约束用于限制一个逻辑门(或一个寄存器)的输出信号所能驱动的总负载电容。它规定了一个输出信号的负载电容的上限。(Sets a maximum capacitance for the nets attached to the specified ports or to all the nets

in a design.)

上述约束的具体数值由工艺厂商提供,但在电路设计中可以进行过约。

transition time is the time needed to transition from one logic state to the other.

set_max_fanout和set_max_capacitance都是对负载进行约束,它们的主要区别在于这两种约束的优化目标。set_max_fanout 约束主要关注电路的时序和延迟,而 set_max_capacitance 约束关注电路的功耗(电路的功耗与负载电容成正比)。

面积约束

DC中的面积约束用于规定电路的逻辑元件在芯片上的最大布局面积,有助于控制设计的复杂性。约束面积的命令示例如下:

1 | set_max_area 100 |

上述命令中100的单位由库单元的面积单位决定,有以下三种单位:两输入与非门个数,晶体管个数,平方微米。

一般会在面积约束时,将最大面积设置为0。因为在DC工具中,默认设置是Timing Constraints比Area Constraints的优先级高,因此DC会在首先保证时序收敛的同时,探索面积最小的综合结果。

时序约束

有很多学习资料将时序约束分析的非常透彻了,这里就暂时跳过了。后面可能会出关于时序约束分析的专题博客,给大家提供一个不错的学习网站,里面的STA分析的较为透彻。VLSI Tutorials

环境约束

在对设计进行优化之前,我们必须定义Design预期运行的环境。通过指定操作条件、系统接口特征和线路负载模型来进行环境约束。操作条件包括温度、电压和工艺变化。系统接口特性包括输入驱动、输入输出负载和扇出负载。环境约束直接影响设计综合效果。

设置操作条件

工艺库中一般提供了几种工作条件的模型以供选择:

- 最好情况(best case):用于对保持时间的时序分析;

- 典型情况(typical case):一般不考虑;

最坏情况(worst case):用于对建立时间的时序分析;

驱动强度

为了准确评估输入接口的时序结果,DC工具需要知道输入接口的驱动强度。驱动强度为Driver阻抗的倒数,输入接口的transition delay为Driver阻抗×输入端口的电容负载。DC默认Driver阻抗为0,即驱动强度为无穷。可以通过

set_driving_cell,set_drive,set_input_transition来对驱动强度进行设置。线负载模型

在DC综合的过程中,net延时是通过设置线负载模型(wire load model)确定的。线负载模型基于net的扇出,对net的电阻电容等寄生参数进行计算。线负载模型的计算函数也是由晶圆厂提供的,晶圆厂则是对使用该工艺流片的芯片的net延时进行统计,从而得到该经验值。

设置线负载模型可以通过“set_wire_load_model”命令完成,也可以让DC自动根据综合出来的模块面积大小选择负载模型。默认情况下是DC自动选择。

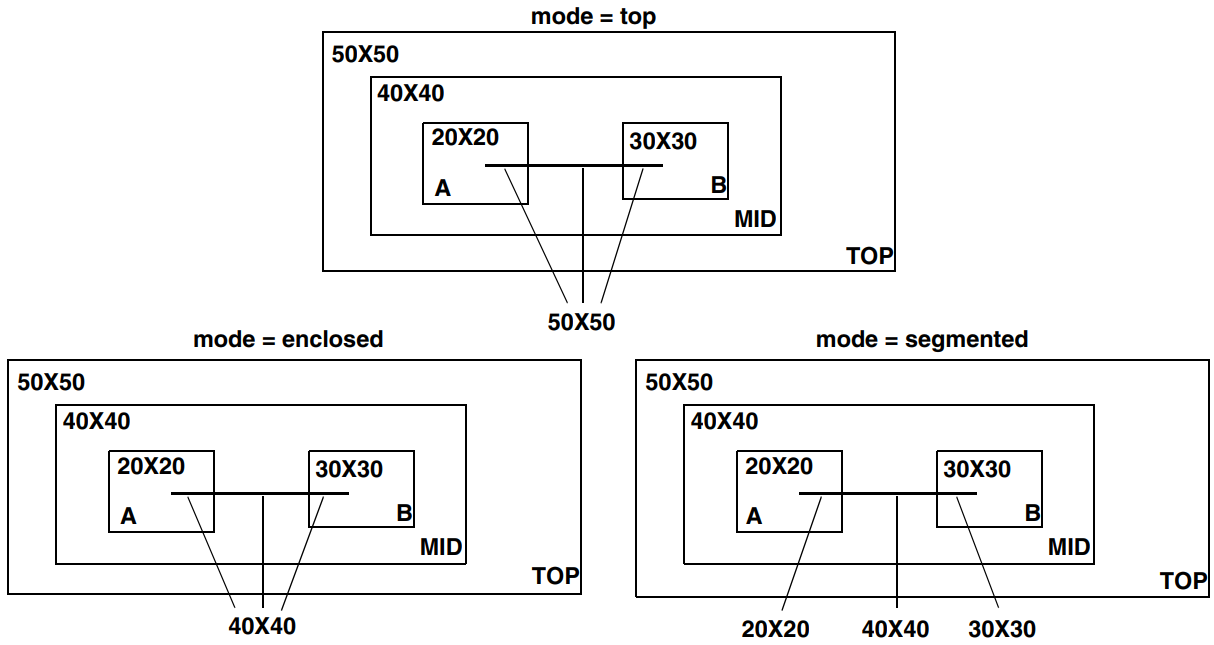

上面说的是模块内的线负载模型,对于模块间的线负载模型,存在一些跨模块的net,它们的wire_load_mode有以下三种决定方式:

顶层(top):所有submodule的线负载模型都用顶层模块的线负载模型代替;

- 围绕(enclosed):net的负载模型用完全包含该net的模块的线负载模型代替;

- 分段(segment):根据net所在的模块,分段对其使用线负载模型进行估计;

输出负载

为了更准确的估计模块输出的时序,除了要知道输出延时之外,还需要知道输出的负载大小。如果输出负载会影响电路的transition time,进而影响时序特性。如果DC默认输出负载为0,即相当于不接负载的情况,这样综合出来的电路时序显然过于乐观,不能反映实际工作情况。

我们可以使用set_load设定load值,例如:

1 | set_load 30 [get_ports OUT1] |

其中“30”的单位可以用report_lib命令进行查看,即Capacitive Load Unit对应的单位。

DC输出结果

- 整个工程以ddc格式保存下来以供后续查看和修改;

- 网表netlist,用于布局布线和仿真;

- sdf文件,标注了用到的标准单元的延迟值,后仿真也需要用到;

- 面积报告,包含时序电路、组合电路和总电路面积;

- 约束报告,给出了综合过程中没有满足要求的约束;

- 时序报告,包含建立时间和保持时间;

- svf文件,包含了DFT和Formality所需的信息,供后续使用;