FPGA与ASIC的区别

FPGA与ASIC的区别

测试逻辑:ASIC要考虑SCAN测试和BIST的问题;(DFT:Design For Test)

存储资源:一般而言,ASIC设计中使用的memory是SRAM与Flop/Latch Array,前端工程师可以根据不同的存储规模选择合适的类型;而FPGA中memory的种类较多且资源受限,一般有Distributed RAM/Block RAM/Ultra RAM等,FPGA设计者一般会在微架构设计中根据存储规模更细致地考虑好各memory使用的资源类型;

计算资源:ASIC设计的计算资源主要采用synopsys designware、其他vendor或者自主设计的IP;而FPGA设计则主要使用片上的DSP单元,DSP单元在FPGA上是hardwired,时序比较好,但功能相对也比较固定,所以FPGA设计者一般会充分DSP单元中固定位宽的乘法器与加法器。在ASIC设计中,累加一般采用加法树设计,而FPGA中则更倾向于使用级联设计,这样可以利用DSP单元间专用的进位布线资源,提高设计的时序;

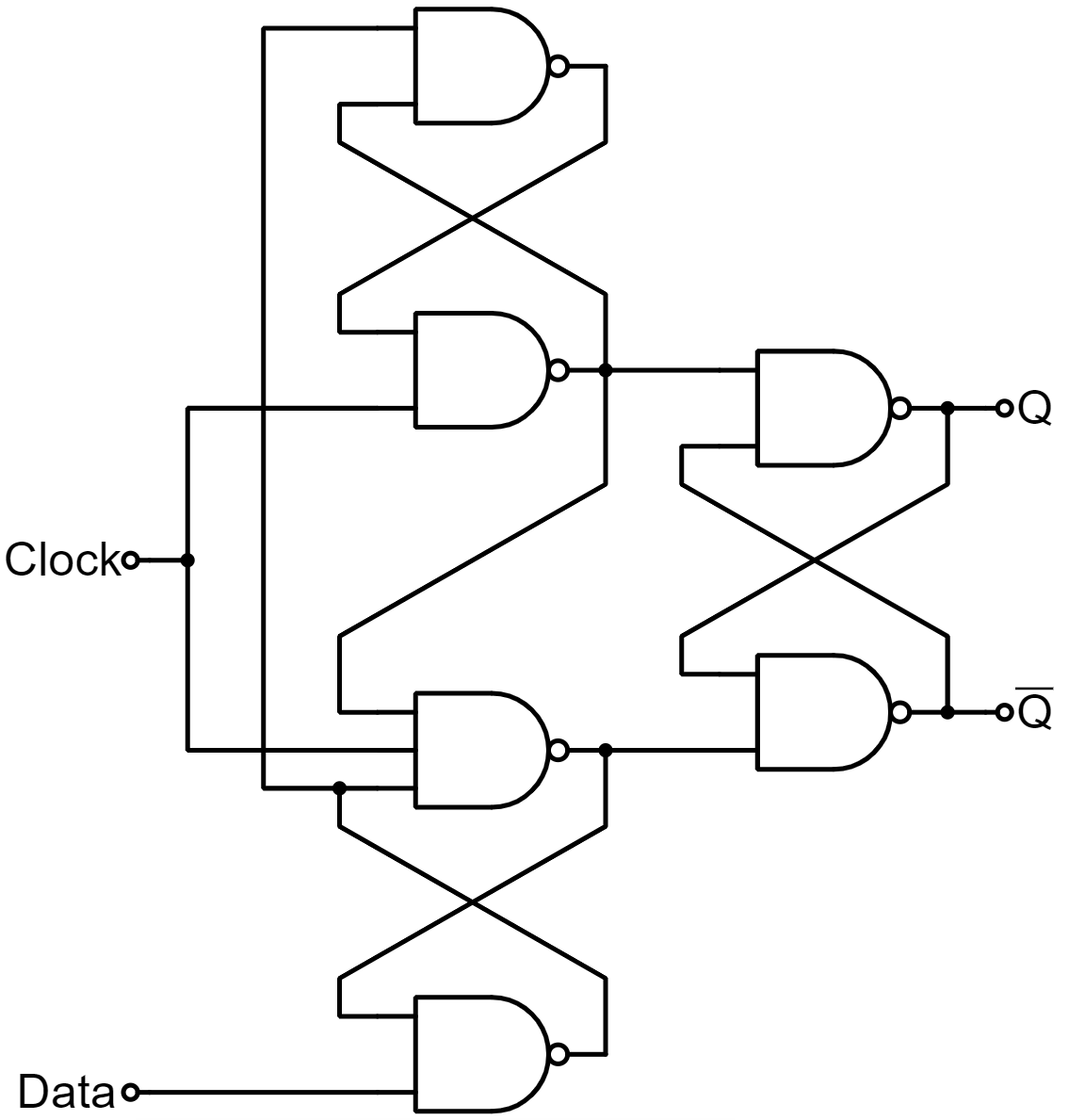

逻辑资源:ASIC设计中的逻辑资源是标准单元库中的logic cell,而FPGA设计中的逻辑资源是CLB中的LUT(4/5/6输入LUT,具体看FPGA型号)与MUX。这里就体现了ASIC和FPGA一个最大区别:估算逻辑深度的方法不同:FPGA没有逻辑深度,就是一个查找表,查找表的深度仅和输入信号的数目有关;而ASIC是有逻辑深度的,在RTL Coding的时候,需要预估逻辑综合出来的级数,哪怕输入信号不多,但逻辑复杂度大的话,也需要拆成2拍;

低功耗设计:ASIC的低功耗设计可以采用clock gating与power gating,但FPGA无法做到power gating,clock信号在FPGA中有专用的布线资源,因此也不建议使用clock gating的方式,但可以用clock enable的方式替代;

时钟复位:clock信号在FPGA中有专用的布线资源,而ASIC内的时钟为了更小的skew会专门进行CTS;ASIC设计中一般使用异步复位,由后端负责处理复位树,FPGA设计中则建议使用同步复位;

FPGA与ASIC在代码层面的区别

ASIC更趋于保守,对逻辑的任何改动都要三思,并要做备选的选择,以防改错,RTL的任何修改几乎都是增量修改;

ASIC对coding style的要求更高,所有模块的coding风格要求一致,这样有利于后端以及后续的check;

ASIC要考虑SCAN测试和BIST的问题,所以设计的时候需要为SRAM做BIST插入,需要为SCAN预留接口;虽然大部分都是工具干的,但是RTL作者也需要手动做一些顶层工作,比如SCAN时钟的来源等逻辑;

ASIC时序预见性更好,可调整度高,所以可以写很大的逻辑;

关键词:保守改动、代码风格、测试逻辑、逻辑级数