修Timing Violation的若干方法

本文转载自探STA|修timing violation的二十一种方法

如有任何版权问题请联系博主。

其实修setup violation和hold violation是对立统一的,例如我们通过insert buffer修一个setup violation,那么有时我们也可以通过remove buffer修一个hold violation。

Fix setup violation

Setup violation的本质是一个时钟周期内上一级寄存器锁存的数据无法正确地传输到下一级寄存器并被正确地锁存,也就是数据跑的太慢了。或者换个思路,是当前寄存器的时钟跑的快了。

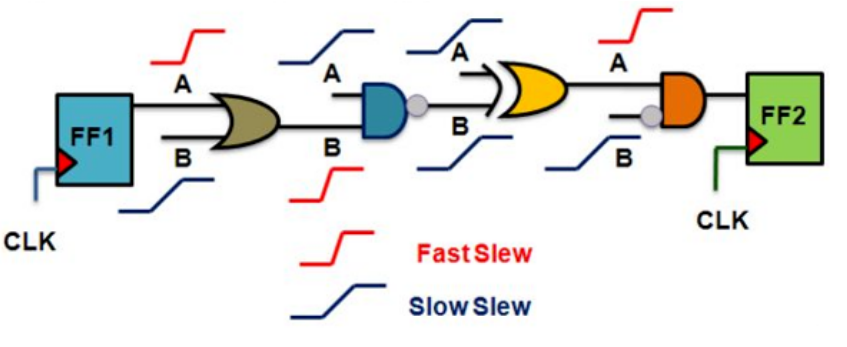

插buffer来fix setup violation主要从信号的slew考虑,减buffer来fix setup violation主要从cell delay的角度考虑。选择何种方式主要看load capacitance。

首先看一下slew的解释,以及与cell delay的相关参数。

A slew rate is defined as a rate of change.

A simple timing model is a linear delay model, where the delay and the output transition time of the cell are represented as linear functions of the two parameters: input transition time and the output load capacitance.

—《Static timing analysis for nanometer designs》

下面两个评论是从插buffer的角度考虑

Buffers increases drive strength of signal and so delay decreases. This is like a repeater in a communication systems . where repeater will re-shape the signal to match it to ideal one and thus time taken by signal to transition from 1->0 and 0->1 decreases.

If you insert the buffer, the signal strength will be improved. This will charge the load Cap fast. When the Cap gets charged fast, you will have less rise & fall delay. This will reduce the delay. That’s it.

下面的评论是从减buffer的角度考虑

Decrese the load Cap. can decrease the cell delay. until the load Cap, is much smaller than the output Cap, of the cell itself, the delay will nearly not change at all. We can call the delay instrinsic delay.

If a timing path consists of cells with instrinsic delay, insert buffer will just increase the delay.

减少Data Path上的Buffer数量

这会减少cell delay。cell级数减少了,这种减小也不是单纯地几何倍数的减小,减小的程度应该是小于remove buffer的数量×原来的cell delay;因为net wire变长之后,电流从net一端传播到net另一端衰减更加严重,对器件的充电速度变慢。

但是该方式会增加net delay,net wire总长度变大,RC参数变大,RC曲线更加绵长。

使用一对inverter替换Buffer

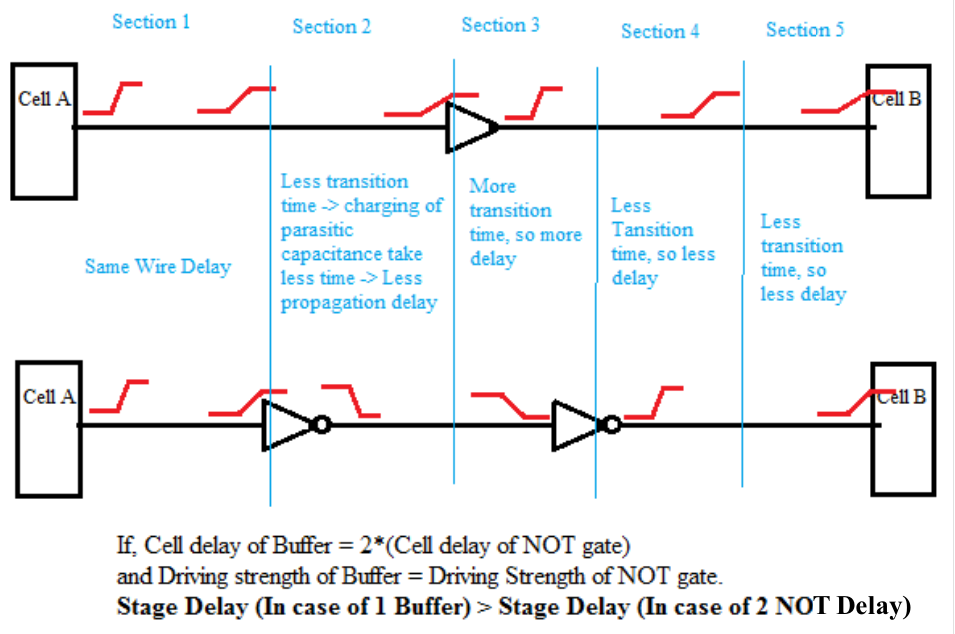

我们知道buffer的结构基本上等价于两个inverter,使用一对inverter替换buffer可以减少data path上总的delay。

和只用一个buffer相比,一对反相器会两倍的减少信号的transition time,这会减少RC delay。而一个buffer的cell delay约等于一对inverter的cell delay,所以总的delay减少了。

Swap VT

这就是换cell的阈值电压(voltage threshold),就是把HVT(High)换成SVT/RVT(Standard/Regular)或者LVT(Low)。

相同情况下low VT的cell的栅极阈值电压更低,所以对于该cell本身其slew更小;相同情况下low VT的cell的栅极导通电流更大,所以其对于后续的net wire的充电速度更快。

所以low VT的cell相当于从cell delay和net delay两种角度去减小了总的delay。

不过,Low VT的cell静态电流更大,静态功耗也更大。

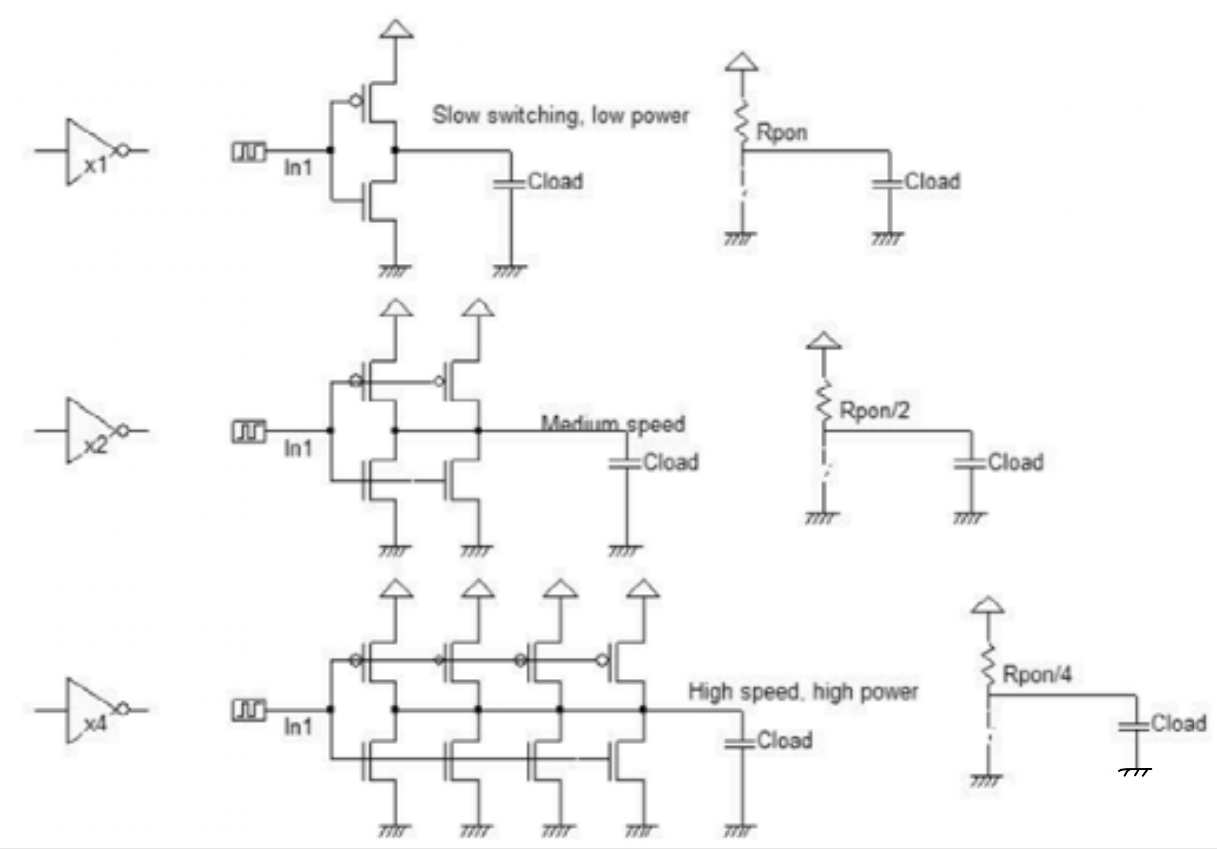

Size-up cell

一般来说大驱动的cell具有更高的speed,但是可能某些cell类型,更大的cell可能速度更慢。

不过,这样也会使得power更高,area更大。

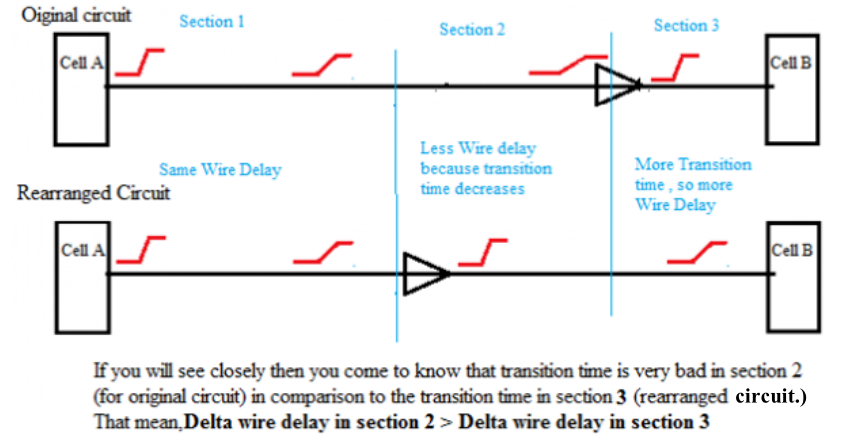

Insert buffer

插buffer会减小transition time,这会减小net delay。如果总的net delay的减小 大于 cell delay的增加;那么总的delay就会减小。

不过,这也会导致power和area增加。

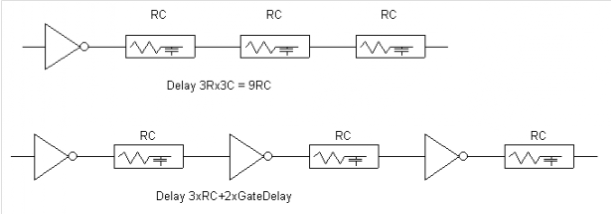

Insert repeater

这跟insert buffer类似,不过区别在于场景的不同。

Long net wire会导致大的RC delay,如果insert repeater可以将net wire切分成多段可以减少总的net delay;因为总的net delay的减少 大于 cell delay的增加,所以这是一种有效的方法。

调整cell在版图的location

本质也是减少net delay.

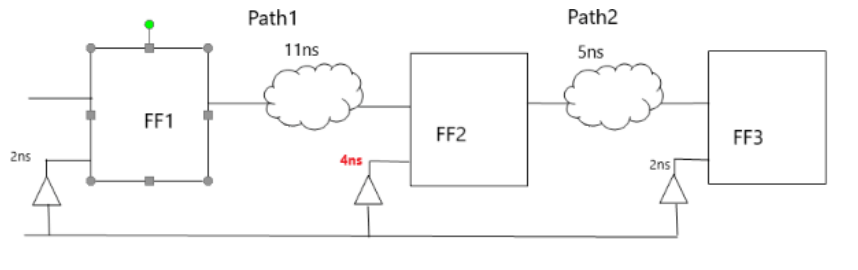

调整clock skew

就是通过skew的调整向后一级接setup的余量。

给critial path用NDR走线

与CTS绕线原理类似,就是减少net wire的RC和cross-talk。

NDR全称是Non default routing rule,非默认绕线规则。默认的绕线规则都是单位宽度,对于clock path或者critial path可以采取双倍宽度的绕线宽度。

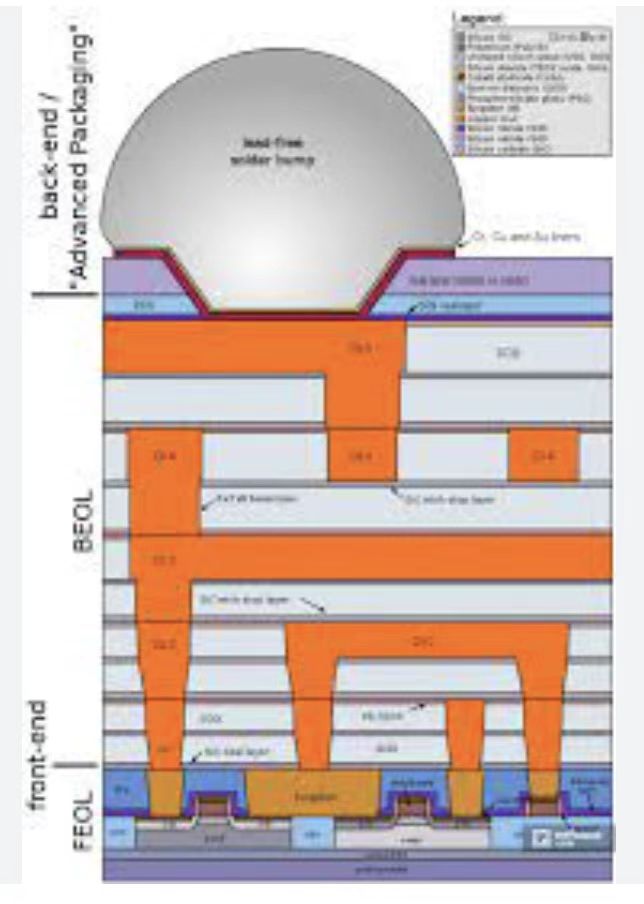

手动走线

手动换高层走线或者手动把net wire捋直。

直观感受一下,上图中橘色的为金属,高层的走线粗,电阻小,所以RC小,delay小。

修crosstalk

修crosstalk除了加shielding和NDR rule以外,还有一种方法是:违例点周围的各种走线remove掉或者拉的远一点。

降频

如果实在修不下去,该降就降吧。

换库

实在不行,也可以选用一些speed更快的库,或者自己定做一些库。

该方法也分全局换库和局部换库,全局就是整个design都换,局部就是让critical path用一些特殊的库。

调整floorplan

通过调整floorplan使得具有交互的module的位置更合理。

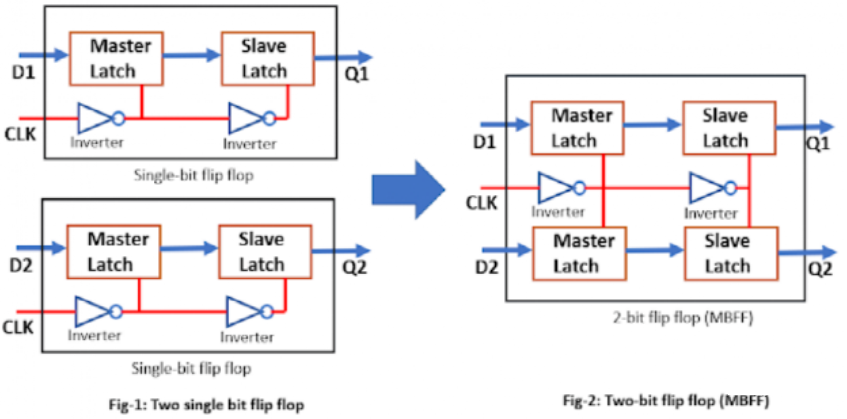

split multi-bit flip-flop

因为MBFF cell内部的公共走线和公共的晶体管更多,所以其本身的load Cap更大,则transition time就更大,delay就更大。因此可以通过拆分MBFF Cell来fix setup violation。

使用PBA代替GBA

GBA 的全称是(Graph Base Analysis)。STA工具计算 timing 时,默认是采用 GBA 模式来报 timing 的,是工具默认的分析方式。它是说工具在从lib中读取cell的delay的时候,永远是读取由最差transition产生的delay。PBA是path based analysis,指的是我要分析哪条timing path,就用这条timing path的transition来查cell的delay。pba算法复杂,分析时间大大提高,但结果更为精确。

打拍

打拍就是在reg2reg path中间再加一个reg,一个周期搞不定的事情,分成两个周期来做。

改RTL

如果RTL综合出来本身的timing path逻辑级数太长或者组合逻辑太多,可以考虑改RTL。

Fix Hold violation

Add Delay

可以使用buffer、inverter pairs、delay cell来修hold violation。

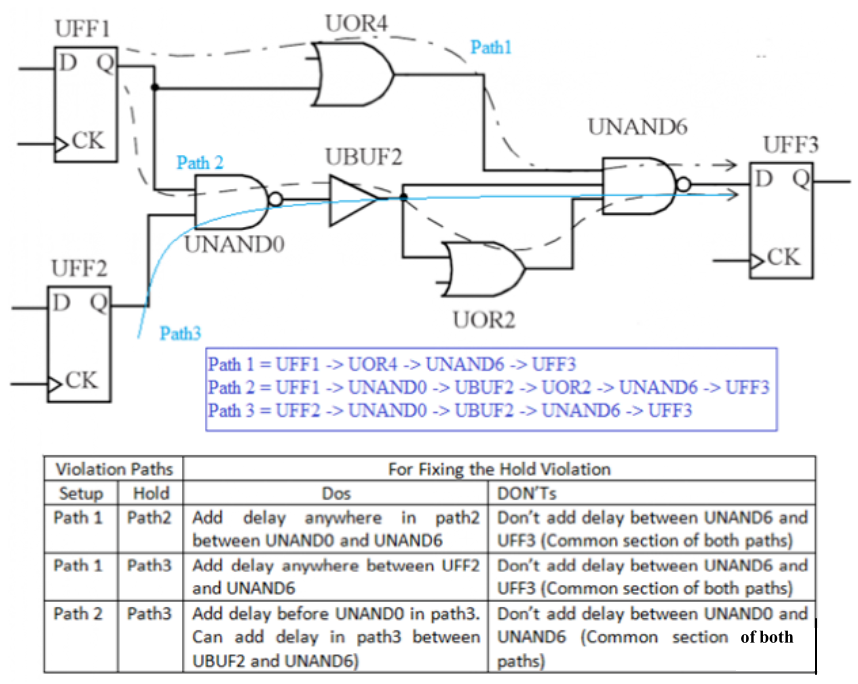

由于hold violation path的start point和end point可能对应着别的setup violation path(或者setup slack比较紧张),所以add delay时需要格外小心。

此外,一般不在两条timing path的common path增加delay。

Size-down cell

尽可能去size end-point附近的cell,这样对别的path影响较小。

另外修crosstalk和手动走线也可修hold。

题外话

有时候面试官会问,流片完了还是有setup/hold violation怎么办,可以从以下角度去考虑回答。

Fix setup violation:降频使用;

Fix hold violation:在setup margin比较足的情况下可以降压,不足的情况下可以降频降压使用;