为什么D触发器需要建立时间和保持时间

为什么D触发器需要建立时间与保持时间

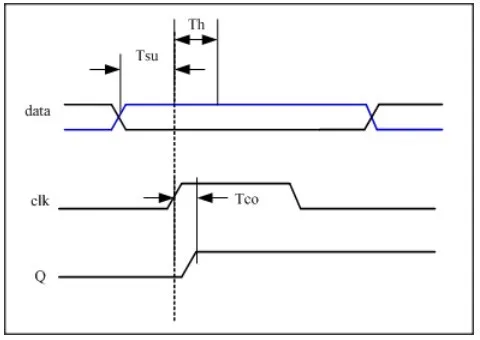

定义

建立时间:时钟有效沿到来之前的某段时间内,数据必须稳定,这段时间称为建立时间,用Tsetup或者Tsu表示。

保持时间:时钟有效沿到来之后的某段时间内,数据必须稳定,这段时间成为保持时间,用Thold或者Th表示。

时序图如下

为什么需要建立时间和保持时间

从CMOS到建立时间和保持时间这篇文章里作者已经讲的很详细了,我就不再赘述锁存器的原理了,大家有疑问的话可以先去看看这篇文章,这里我只简单举例记录一下我个人对建立时间和保持时间的理解。

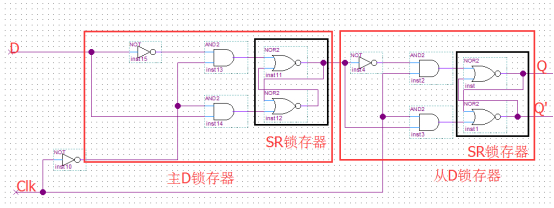

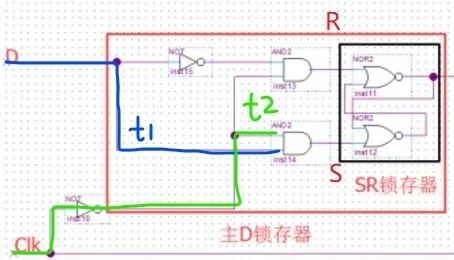

我们从D触发器的门级电路开始分析,D触发器的门级电路如下:

D触发器在时钟(上升)边沿进行数据的锁存。我们这里假设原来的输出是1,即从锁存器锁存的数据为1,要锁存的数据是0,来理解建立时间和保持时间。

要让时钟上升沿之后Q输出为0,即让从锁存器的输出变为0,也就是要让主锁存器在时钟上升沿之后稳定地锁存住0。

总结而言,在上升沿到来及到来之后,主锁存器负责锁存数据,而从锁存器负责传输主锁存器所锁存好的数据。这样一来,我们重点分析主锁存器即可。

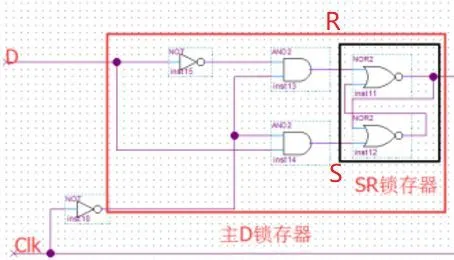

主锁存器的门级电路:

1、如果数据的建立时间不足,会发生什么?

按我们的假设,也就是数据(0)相对于时钟上升沿来的晚了。假设在T=0ns的时候,clk从0变成1(为方便分析,假设时钟理想无跳变延时)。我们假设一个数据D1=0在T=-0.7ns(即比时钟上升沿提前0.7s)的时候到达数据的端口,然后另一个数据D2=0在T=-0.3ns的时候才来到数据端口(即D1来得早,而D2来得比较晚不满足建立时间的要求)。我们看看D1的路线,首先经过反相器变为1,然后经过与门(此时时钟还是低电平,该与门的另一个输入为1)变成1,经过或非门之后,将输出Q变成了0。

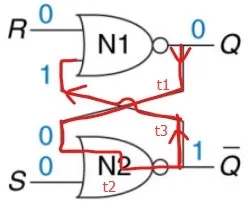

但此时主锁存器输出的Q还不稳定,需要通过反馈改变或非门的输入才能保持输出数据的稳定。如下图所示,通过反馈使得自己或非门的输入为1才能维持Q的稳定,需要t1+t2+t3的时间。

我们再回过头看D2这个数据,它提前于时钟沿的时间不多,刚经过与门时钟沿就来了,没有成功通过反馈到达或非门的输入,不能稳定锁存住从锁存器要锁存的0值,这就是建立时间不足引起的锁存不住值导致亚稳态的原因。

2、如果数据的保持时间不足,会发生什么?

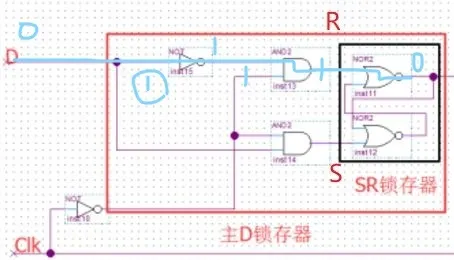

我们看保持时间仍要从主锁存器这边看:

假设T=0时刻时钟Clk发生从0->1的上升沿跳变,Clk的高电平信号首先要经过反相器变成0信号后传到后面的与门,如上图绿线所示路径,假设该路径延迟时间为t2,也就是说t2时刻与门的输入就为低电平0,那么在t2时刻之前,与门的Clk输入端始终保持高电平1。

在t2之前,如果输入端D发生跳变(按我们的假设,从0变为1,即数据的保持时间不足),变换后的数据端高电平经过t1延迟时间后(上图蓝线所示路径),到达与门的另一个输入端。

一般情况下,由于时钟信号需要经过反相器,所以t2>t1,那么与门的输出在t1~t2时刻之间的时候输出为1。也就是SR锁存器的置位端为1,这会导致Q=1,这与我们要锁存的0值不同,导致亚稳态的出现。

总结

建立时间:在时钟上升沿到来之前主锁存器将数据稳定锁存所需的时间。

保持时间:在时钟上升沿到来之后主锁存器传输门关断至锁存数据的时间。