Vivado中RTL封装IP流程

Vivado中RTL封装IP流程

前言

本文记录自己将RTL代码封装成IP的流程,以供之后查阅使用。最近一个月在做一个数据仲裁与转发的项目,已经完成功能仿真,准备将其封装成IP在Block Design中进行调用。实验平台为Vivado 2018.3,编程语言为Verilog,IP的接口主要是一个AXI-Lite接口和一个AXI-Full接口。闲言少叙,我们直接开始。

详细流程

准备工作

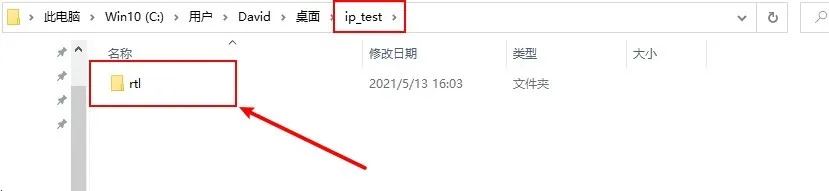

新建一个文件夹ip_test,在该文件夹下新建文件夹rtl,将所有RTL源码放入该文件夹,完成准备工作;

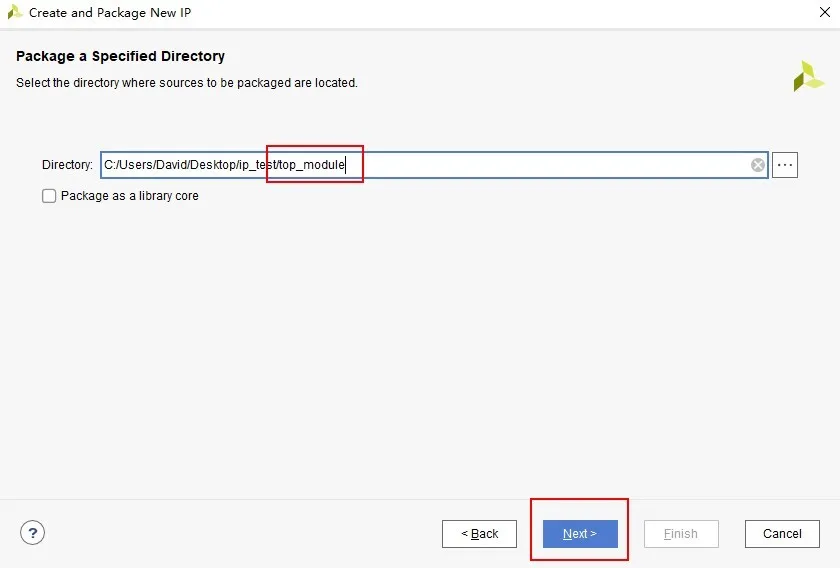

新建一个文件夹top_module,里面仅存放RTL源码的最顶层的.v文件,便于IP生成正确的接口。(之前尝试将所有的RTL源码一次导入,发现vivado不能正确识别顶层模块,从而导致IP接口一直不对)

创建工程

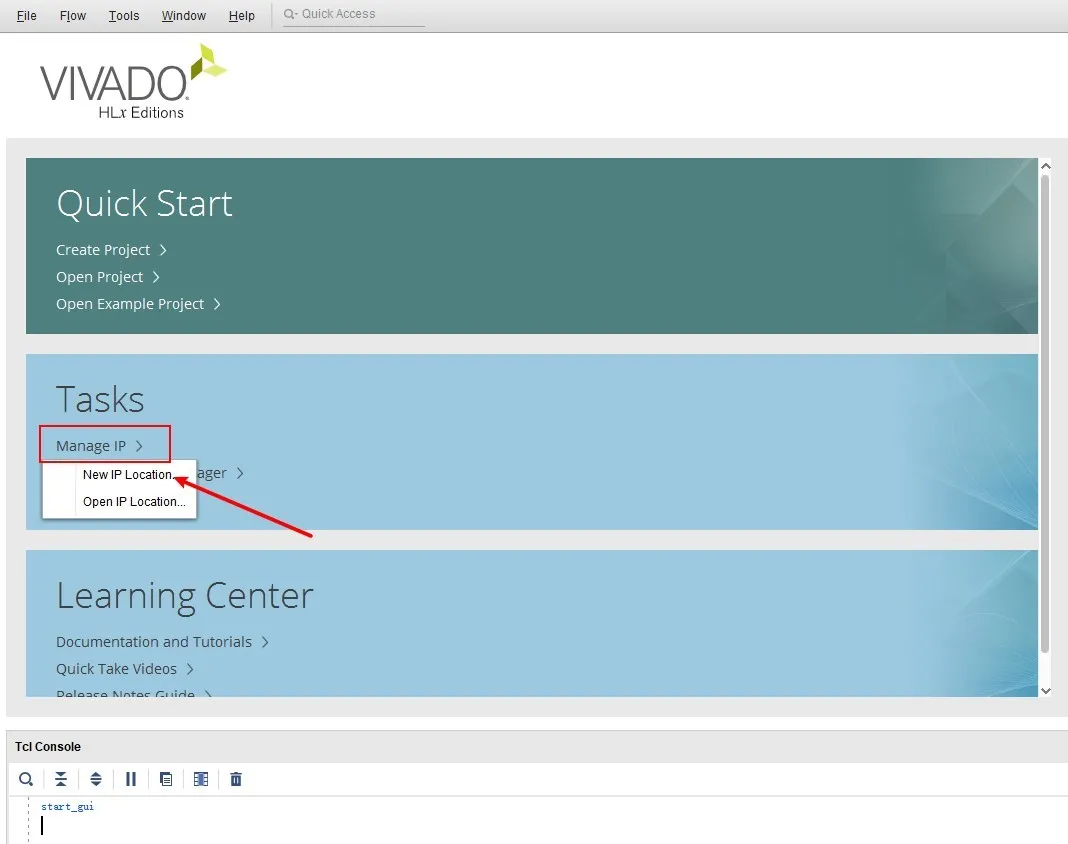

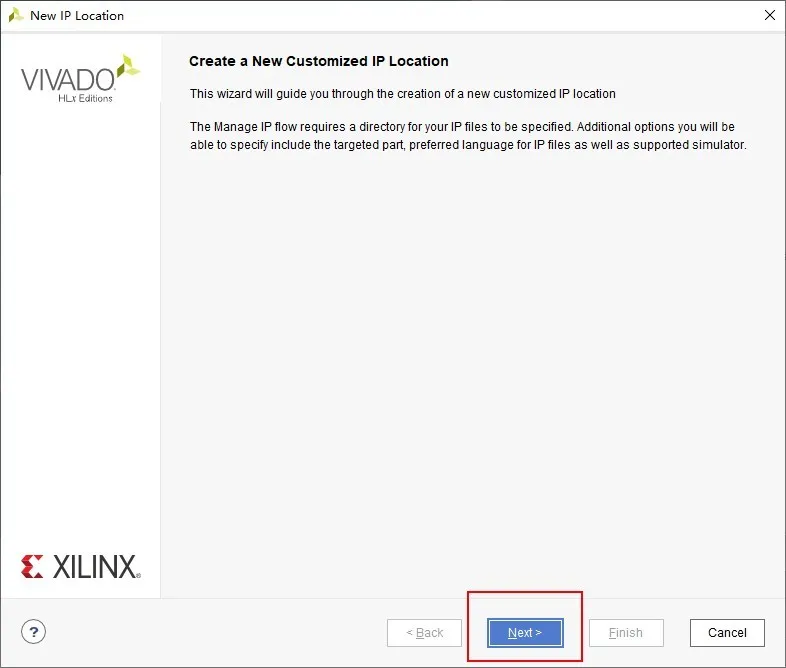

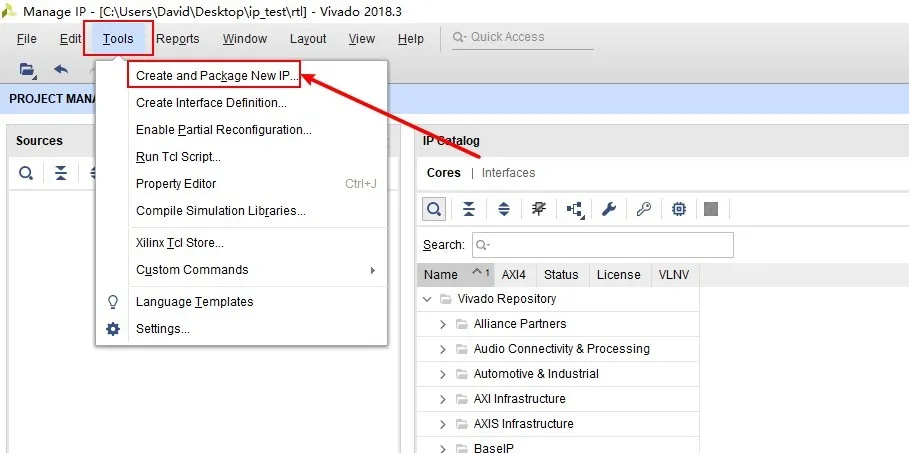

双击打开vivado 2018.3,选择Tasks->Manage IP->New IP Location,按下图所示顺序进行操作;

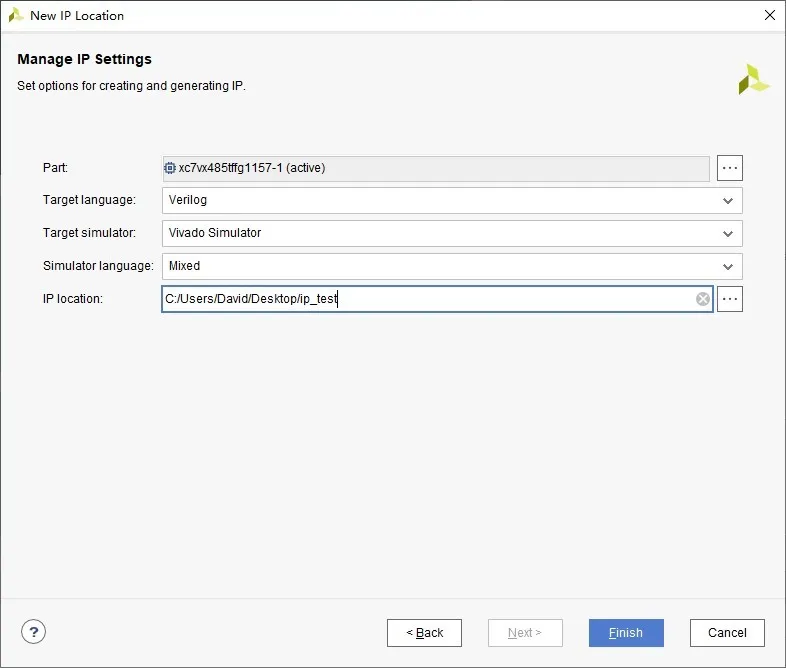

上图中的IP location选择之前建立的ip_test文件夹路径,选完后点击Finish完成工程的创建;

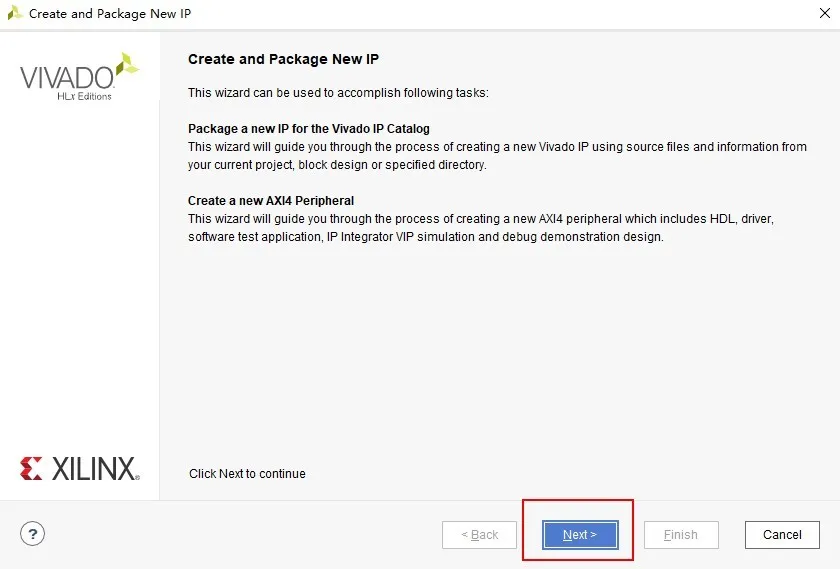

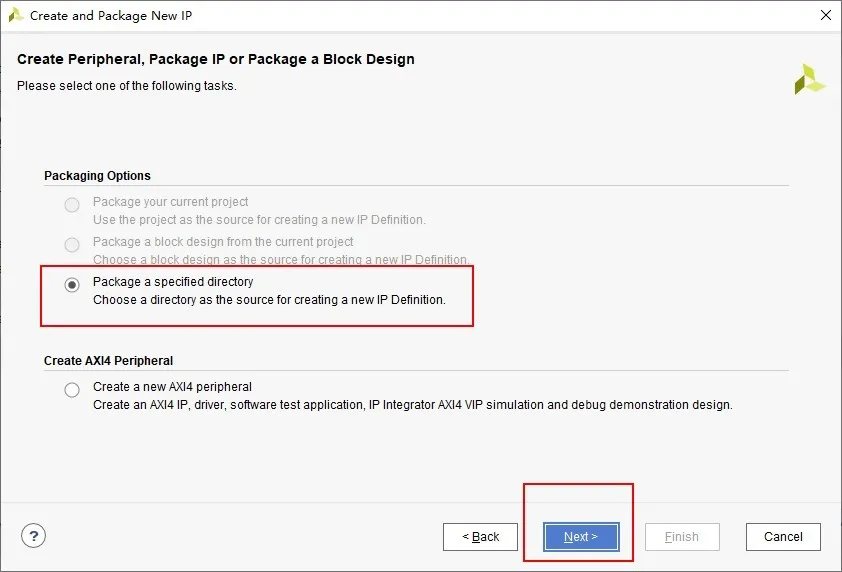

因为本项目已有RTL源码,所以上图中我们选Package a specified directory;如果没有源码想创建一个带AXI接口的空IP往里写功能的话就选择Create a new AXI4 Peripheral;

此处一定注意下图中的路径,选择RTL顶层模块源码的路径

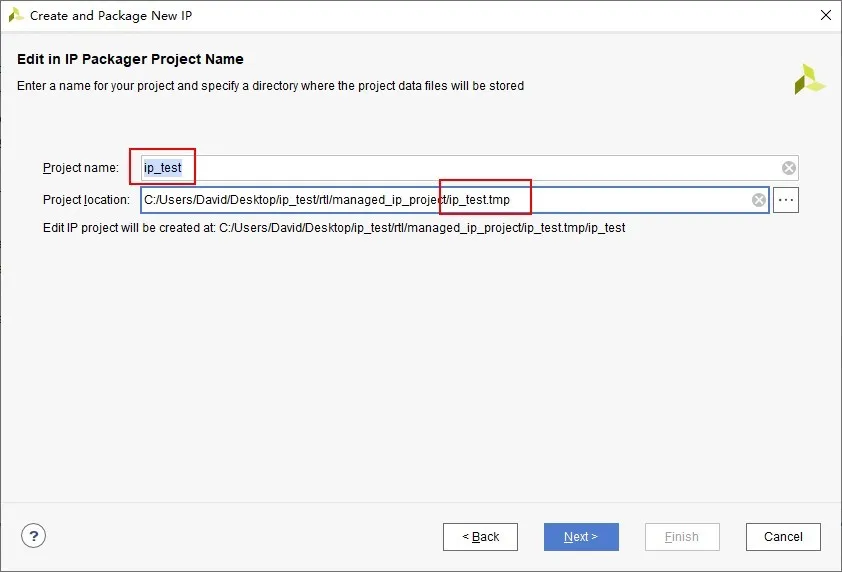

指定项目的名称,本示例工程名字为ip_test;

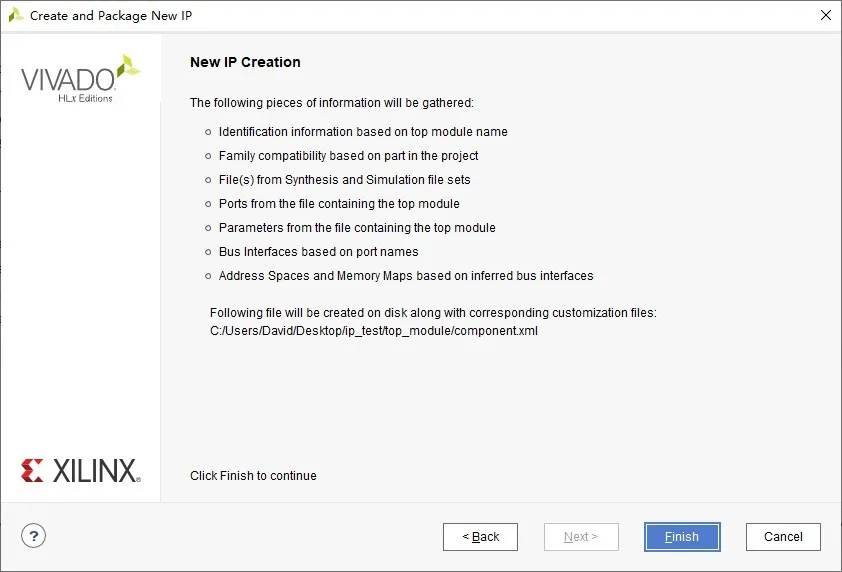

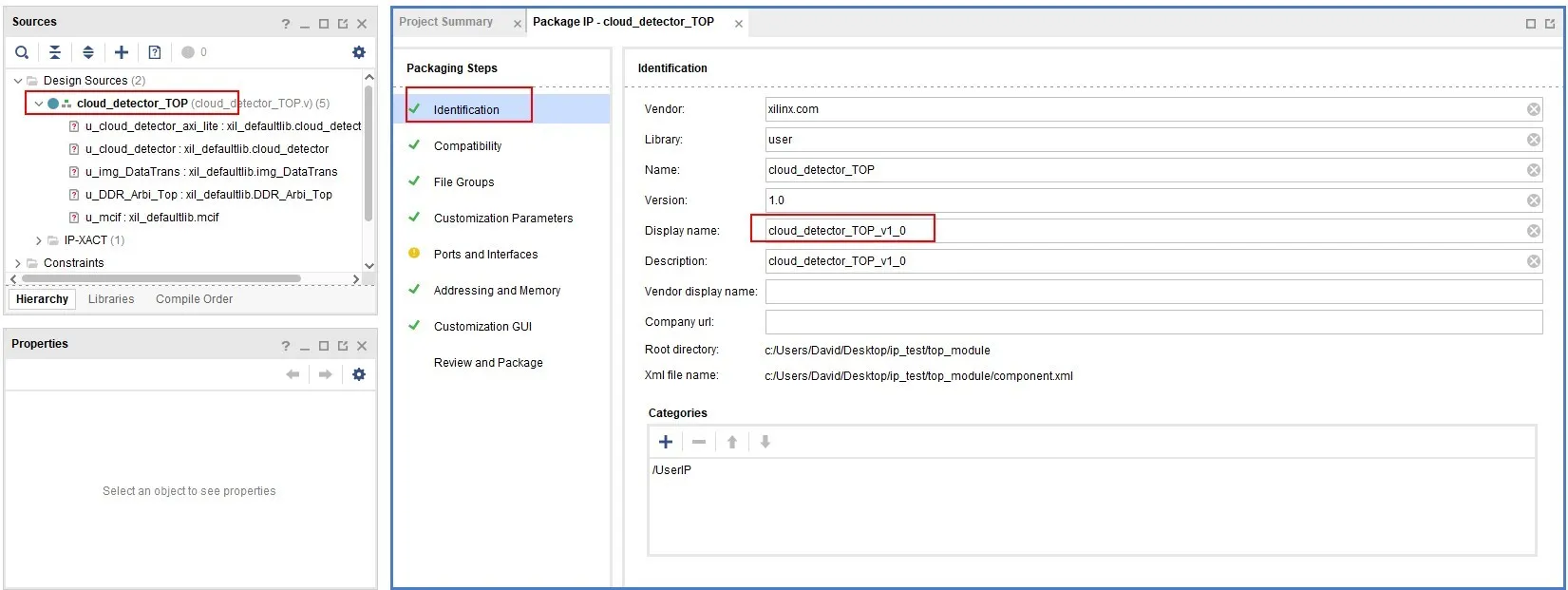

点击Finish后我们看到封装IP的界面,此时看到IP的名称与顶层模块相同,且接口也与顶层模块的一致,只是此时除了顶层模块外,其余模块均未添加到Design Sources中。

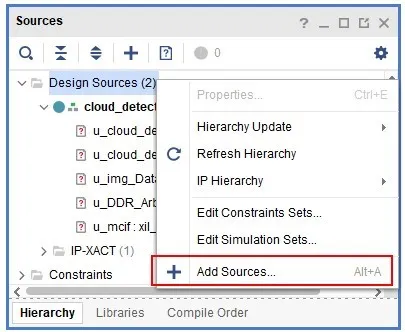

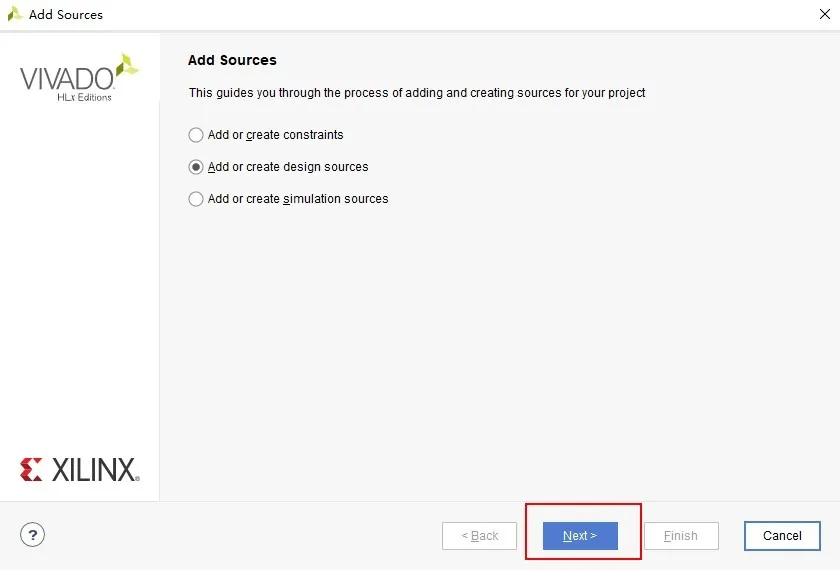

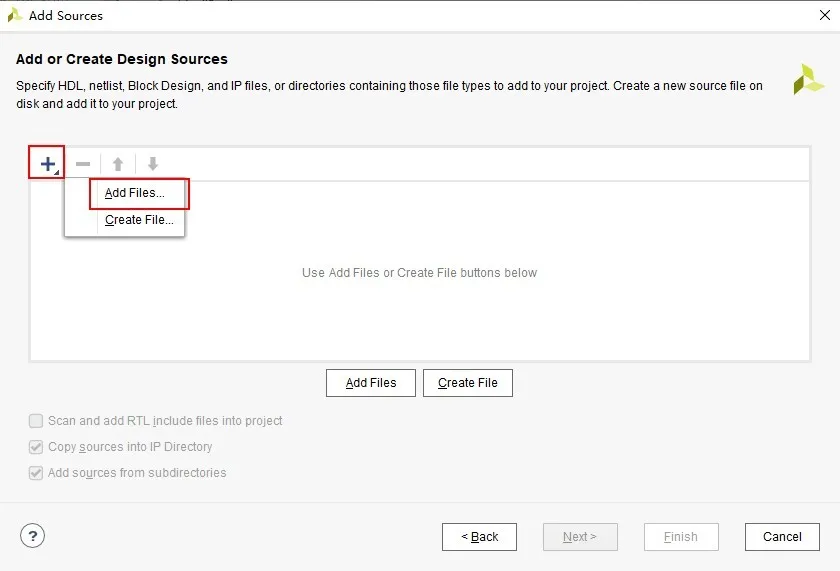

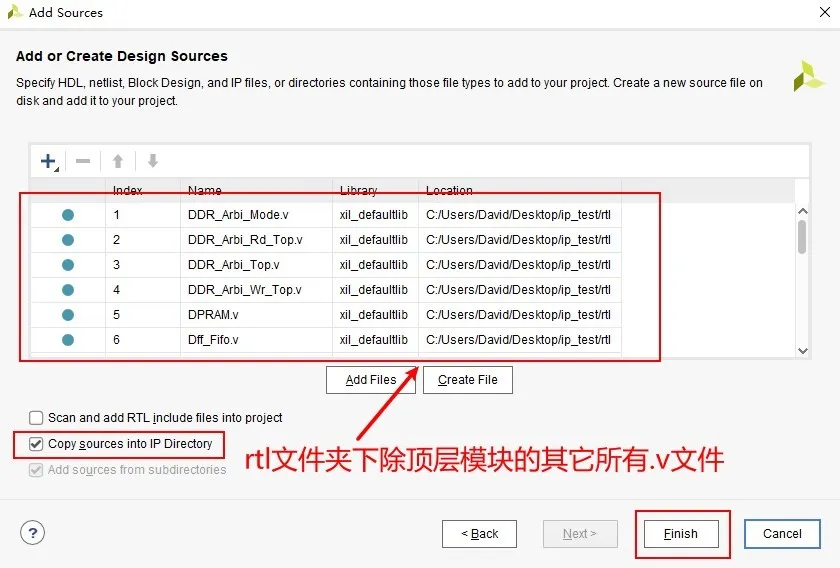

下面进行剩余源码的添加,将rtl文件夹中的代码添加到Design Sources中。

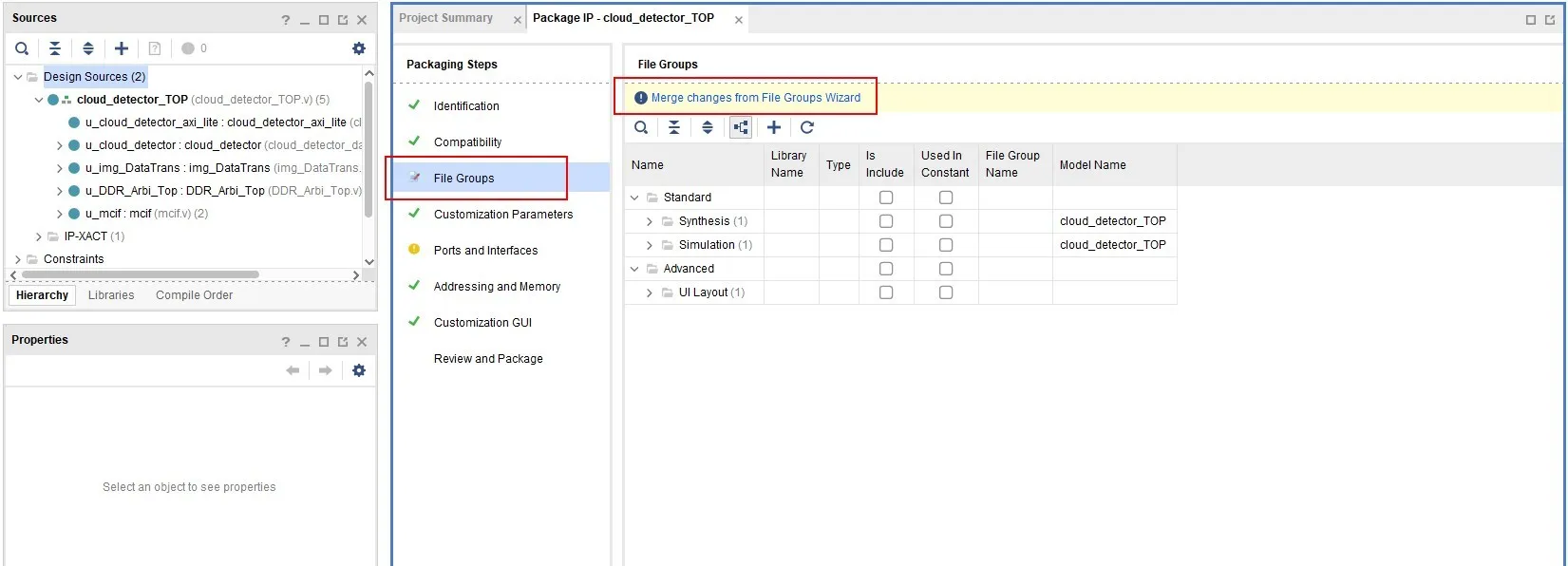

选择IP封装模块的File Groups选项,点击Merge changes from File Groups Wizard

可以看到此时的IP已经包含了所有的源码;

属性配置

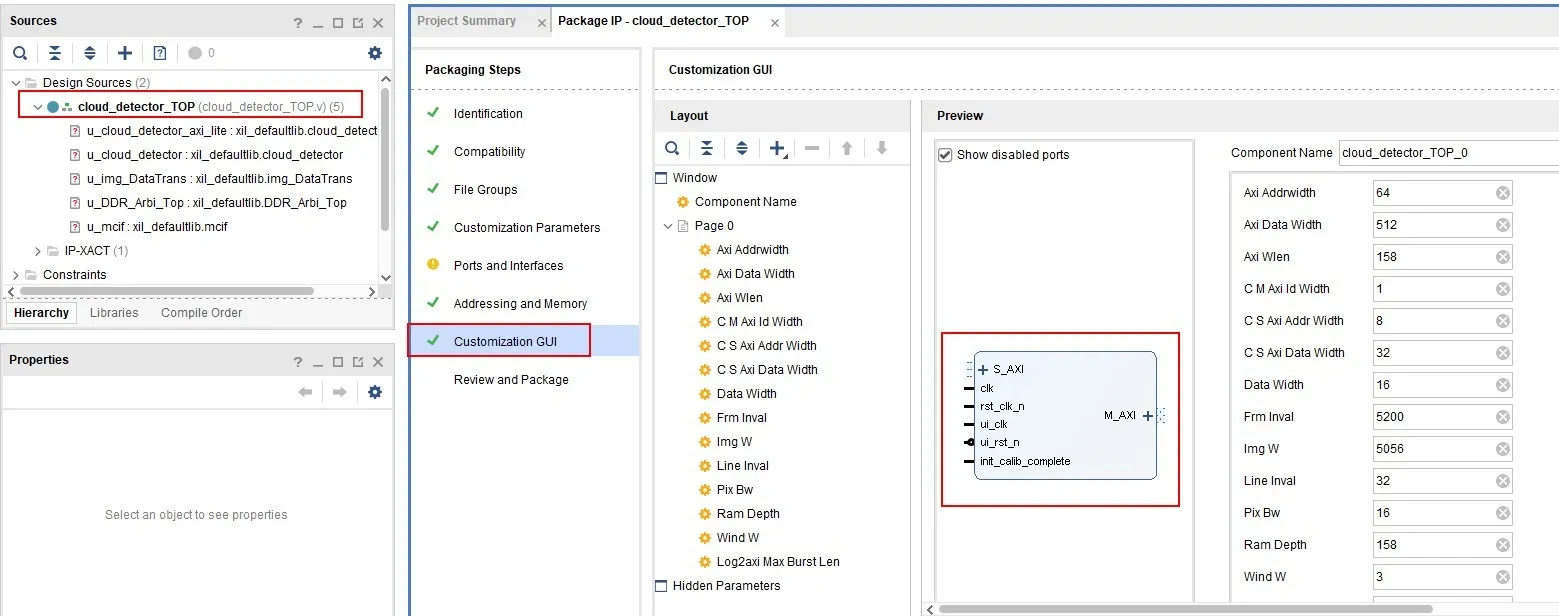

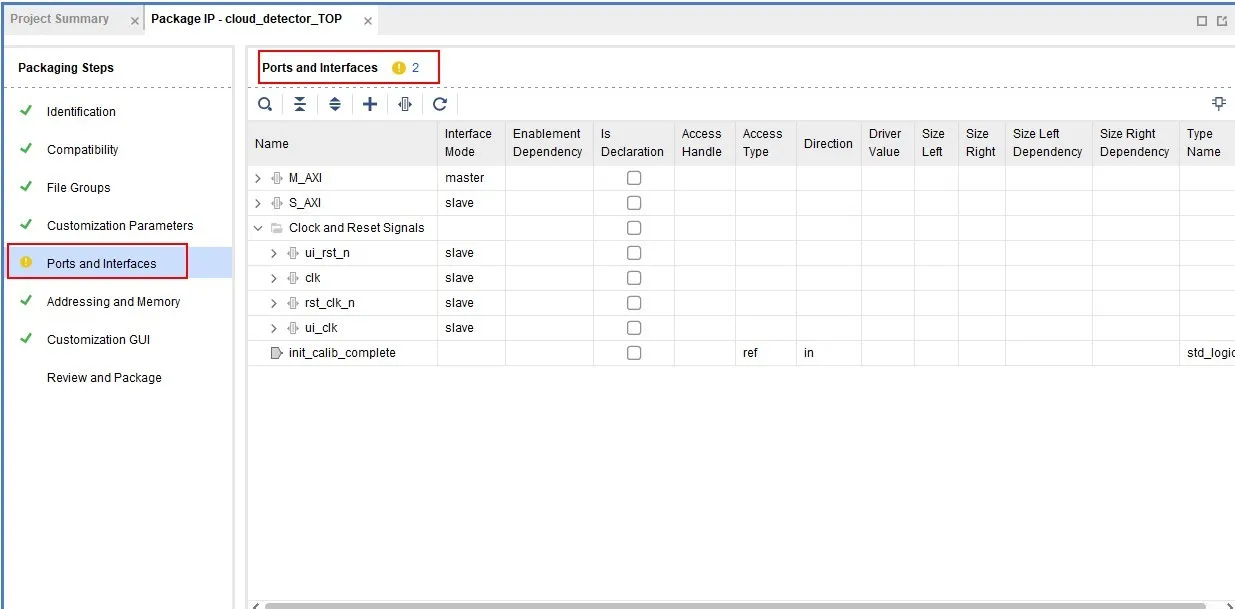

在Ports and Interfaces界面中,我们可以看到,vivado工具自动将时钟复位信号、AXI-Full信号和AXI-Lite信号进行打包处理(vivado永远的神!),但还有一些属性需要设置,否则vivado会报warning。如复位信号的低电平复位属性、时钟与AXI协议的相关属性等;

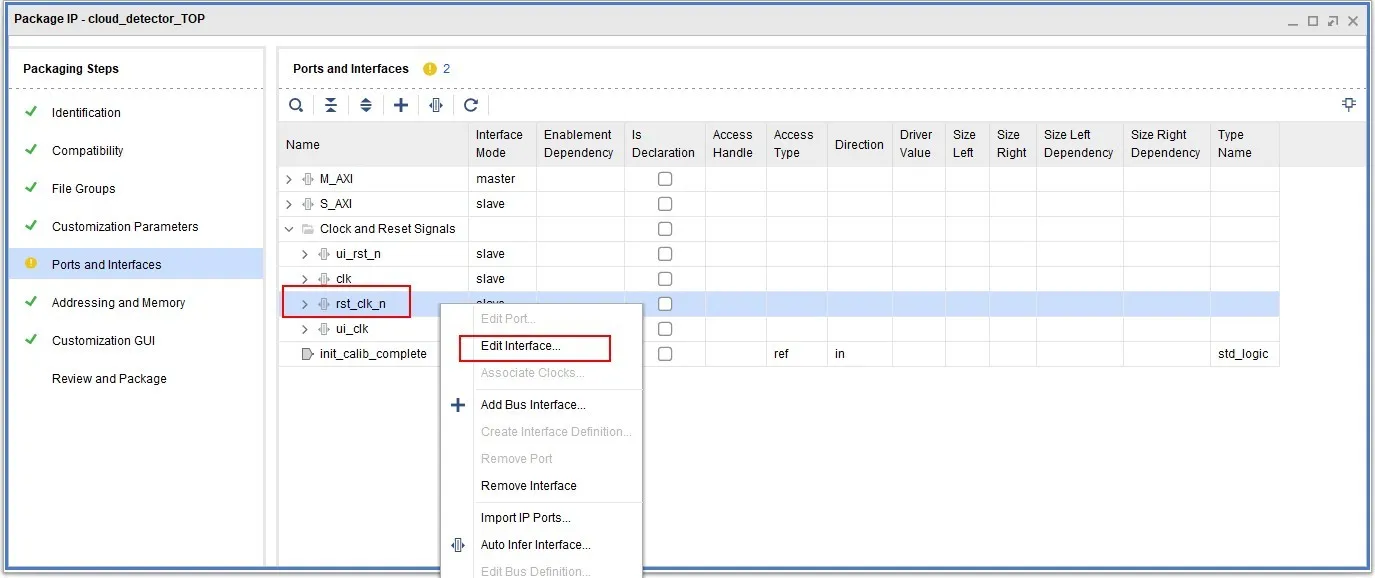

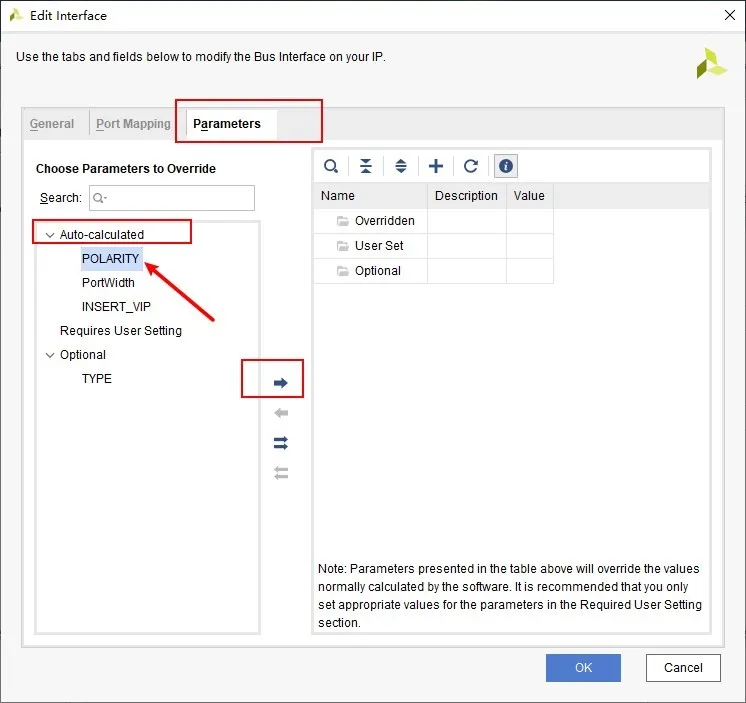

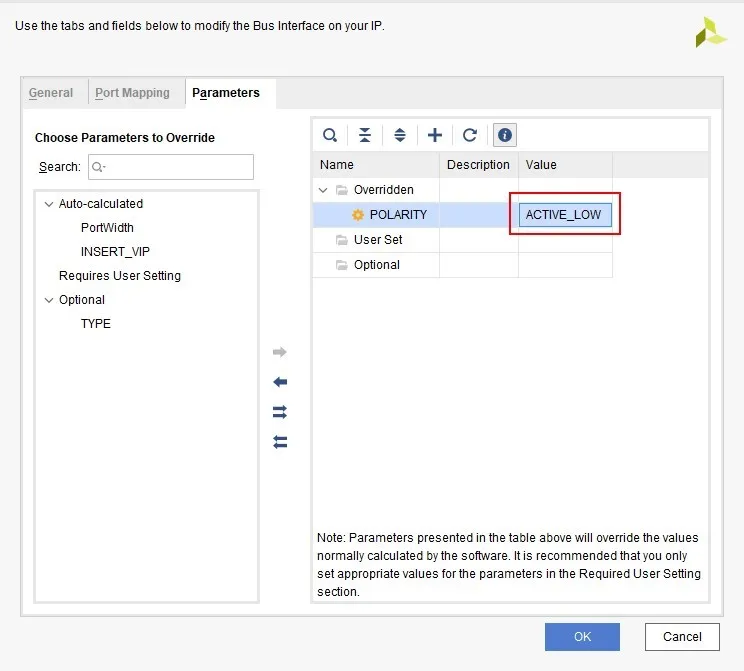

添加复位信号的低电平复位属性流程如下:

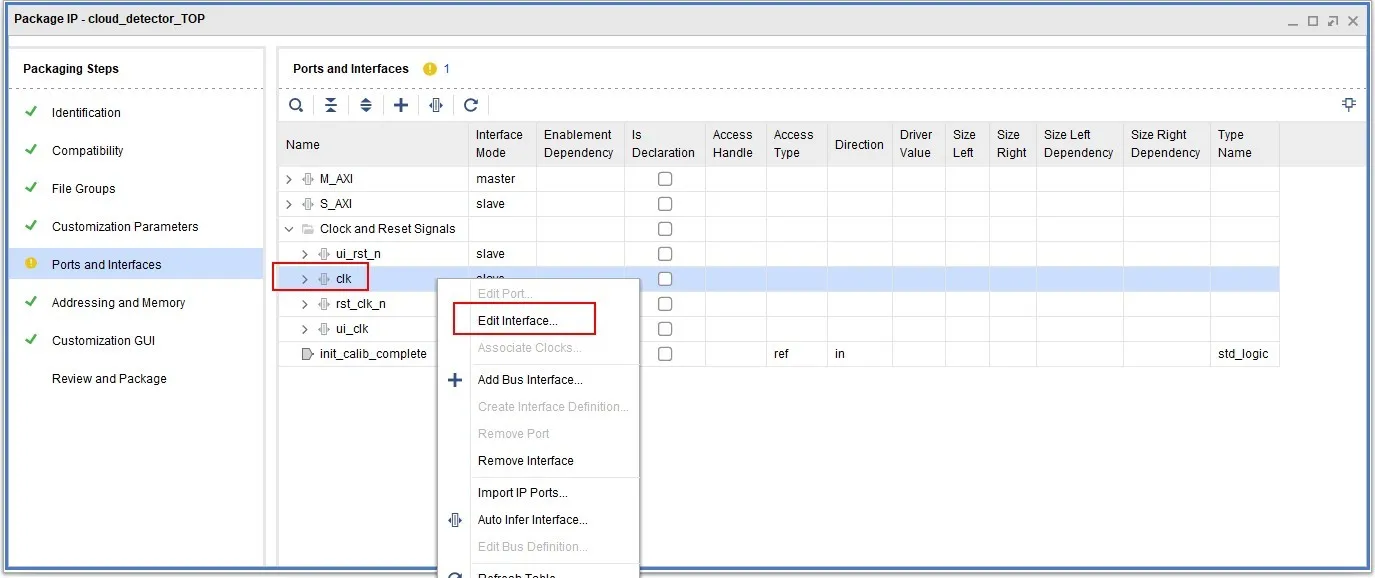

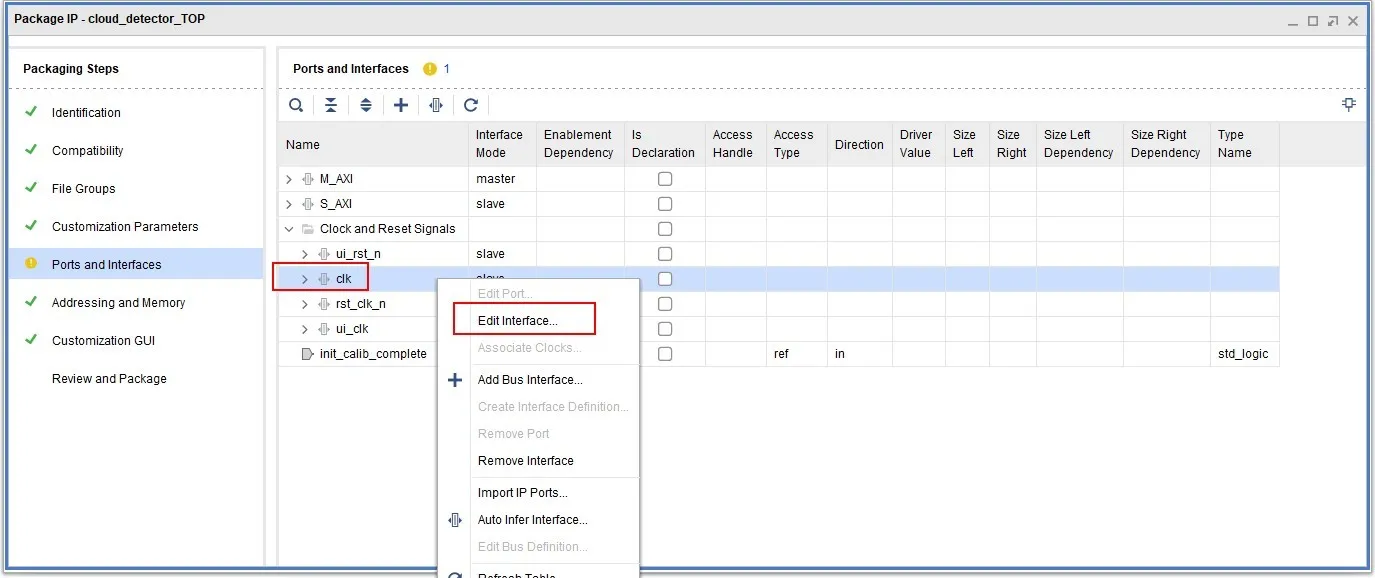

将clk时钟与rst_clk_n绑定起来,并指定AXI-Lite接口用clk时钟

具体各参数的属性配置情况大家可以参考vivado官方教程ug1118。完成上面时钟或者复位的绑定配置后,最后进行IP核的导出。

导出IP

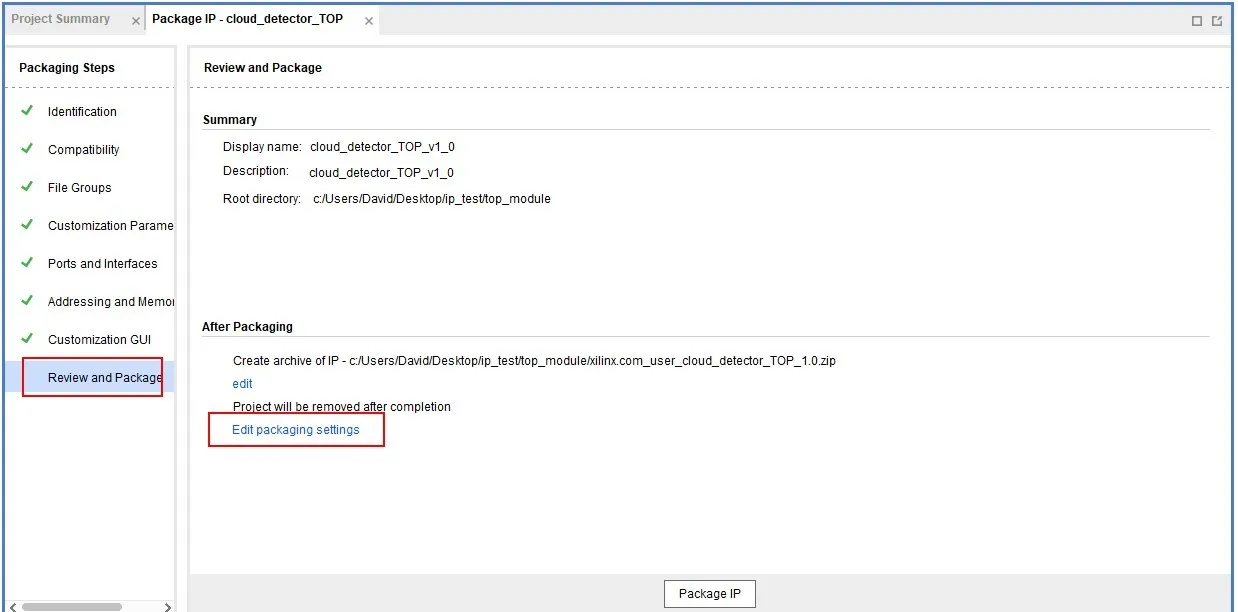

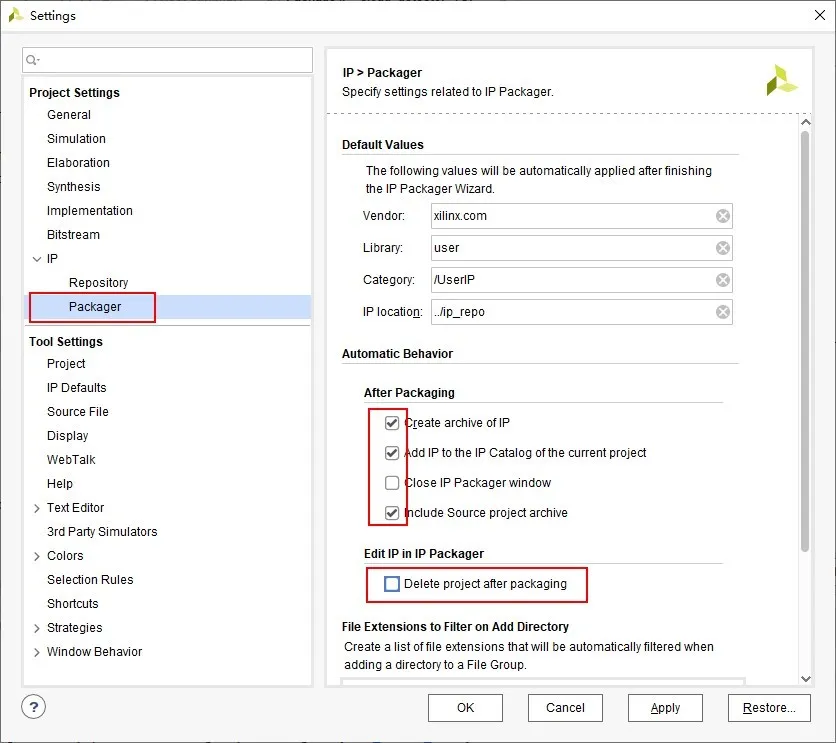

在封装IP界面选择Review and Package,先进行打包IP的配置,点击Edit packaging settings;

进行上图所示的配置,其中Delete project after packaging选项可以不选,因为导出IP可能之后还要继续,要对RTL代码进行修改上板测试来迭代更新,所以我们一般保留导出IP的项目工程。

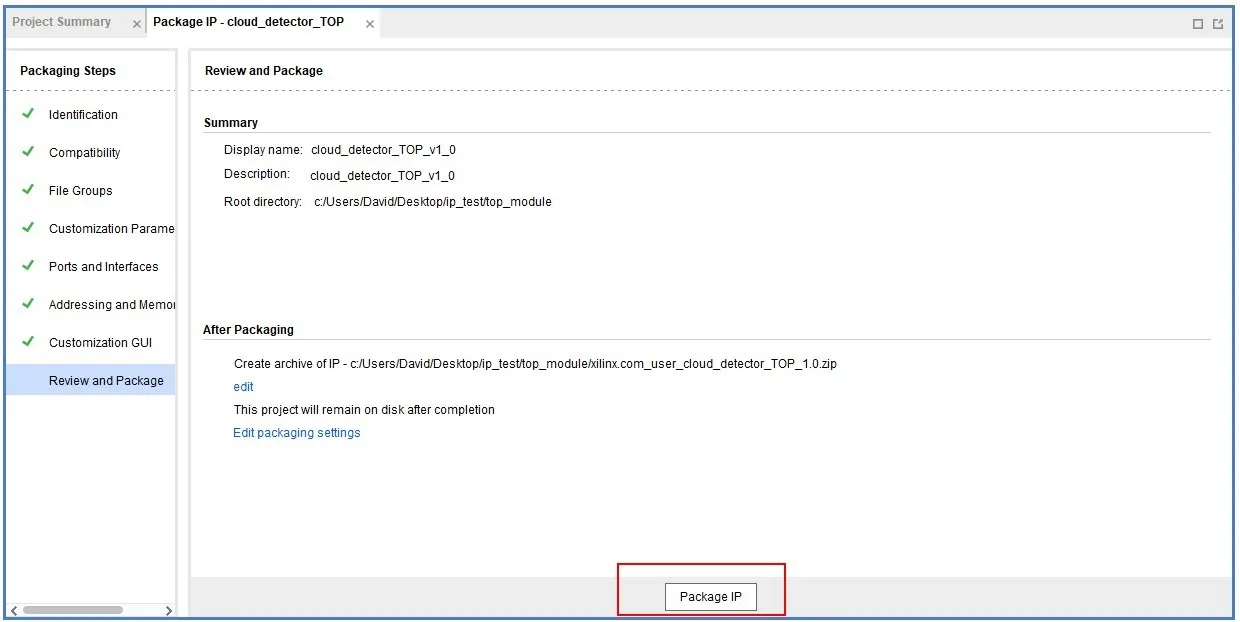

最后回到封装IP的界面,点击Package IP选项即可。

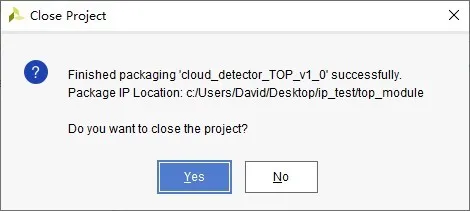

已经成功打包,询问是否关闭项目工程,Yes或者No均可。

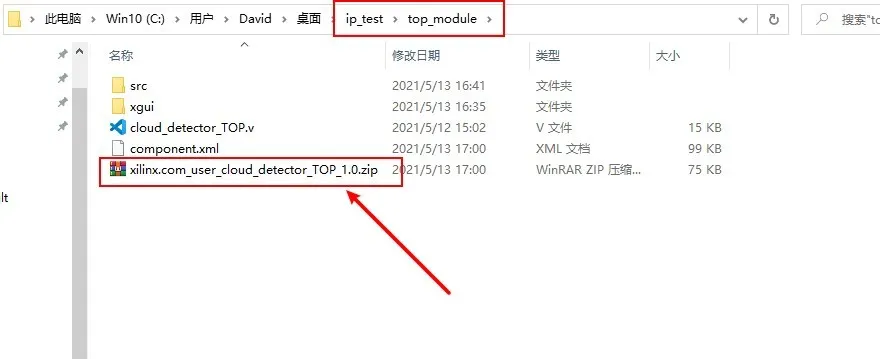

到指定的路径下查看,发现已经生成我们所需的IP。至此,封装IP圆满结束。

结语

本文为笔者打包IP的经验分享帖,其中不免错误不足之处,如果其中步骤有误还望大家指正出来,一起交流进步。

参考资料

Vivado Design Suite User Guide: Creating and Packaging Custom IP (UG1118)