半加器、全加器和行波进位加法器原理与设计

HDLBits链接

半加器

定义:

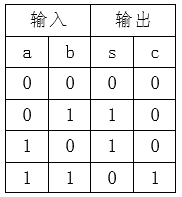

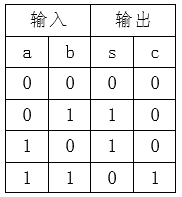

半加器用于计算2个单比特二进制数a与b的和,输出结果sum(s)和进位carry(c)。在多比特数的计算中,进位c将作为下一相邻比特的加法运算中。其真值表如下所示。

题目描述:实现一个半加器。半加器将两位比特相加(不带进位)并产生一个1bit结果和一个进位。

Solution:

1

2

3

4

5

6

| module top_module(

input a, b,

output cout, sum );

assign {cout,sum} = a + b;

endmodule

|

全加器

定义:

全加器不同于半加器的地方是,全加器带有进位cin。输入为a,b,cin, 输出为sum(s)和carry*(cout),均是单比特信号。s为a,b,cin三个单比特数的和,cout为a,b,cin三个数超过2后的进位。

题目描述:实现一个全加器。全加器将两位比特相加(带进位)并产生一个1bit结果和一个进位。

Solution:

1

2

3

4

5

| module top_module(

input a, b, cin,

output cout, sum );

assign {cout,sum} = a + b + cin;

endmodule

|

行波进位加法器

定义:N-bit加法器可以根据1-bit全加器组合而成。每个全加器的输出进位cout作为下一个全加器的输入进位cin,这种加法器称为行波进位加法器(Ripple-carry adder,简称RCA)。

题目描述:现在我们已经知道如何实现一个全加器,我们将使用它的3个实例来创建一个3位二进制的行波进位加法器。

行波进位加法器将两个3位数字和一个进位相加以产生一个3位结果和一个进位输出。

Solution:

1

2

3

4

5

6

7

8

9

| module top_module(

input [2:0] a, b,

input cin,

output [2:0] cout,

output [2:0] sum );

assign {cout[0],sum[0]} = a[0] + b[0] +cin;

assign {cout[1],sum[1]} = a[1] + b[1] +cout[0];

assign {cout[2],sum[2]} = a[2] + b[2] +cout[1];

endmodule

|

巩固练习

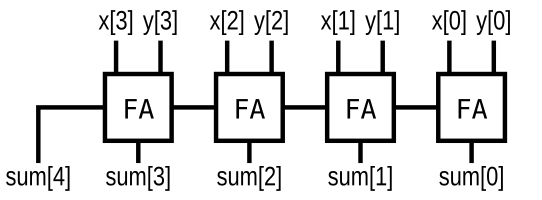

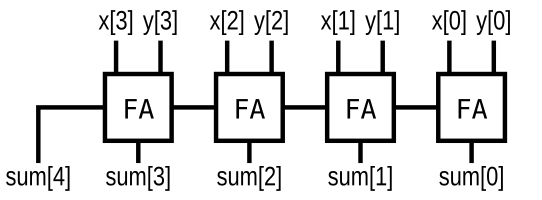

题目描述1:实现下图所示电路,其中“FA”指全加器(Full Adder)。

Solution1:

1

2

3

4

5

6

7

8

9

10

11

12

13

| module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum);

wire [2:0] cout;

assign {cout[0],sum[0]} = x[0] + y[0];

assign {cout[1],sum[1]} = x[1] + y[1] + cout[0];

assign {cout[2],sum[2]} = x[2] + y[2] + cout[1];

assign {sum[4],sum[3]} = x[3] + y[3] + cout[2];

endmodule

|

题目描述2:

假设有两个8位数字的补码,a[7:0]和b[7:0]。这俩数字相加产生s[7:0]。模块中需计算是否发生了(有符号的)溢出。

tips:当两个正数相加产生一个负结果,或两个负数相加产生一个正结果时,会发生符号溢出现象。有几种检测溢出的方法:可以通过比较输入和输出数字的符号来计算溢出,或者从n位和n-1位的进位来判断是否溢出。

Solution2:

1

2

3

4

5

6

7

8

9

10

11

| module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

);

assign s = a + b;

assign overflow = (a[7]&b[7]&~s[7]) | ((~a[7])&(~b[7])&s[7]);

endmodule

|

题目描述3:创建一个100位的二进制加法器。加法器将两个100位的数和一个进位相加产生一个100位的结果和一个进位。

Solution3:

1

2

3

4

5

6

7

8

9

| module top_module(

input [99:0] a, b,

input cin,

output cout,

output [99:0] sum );

assign {cout,sum[99:0]} = a + b + cin;

endmodule

|

题目描述4:

已有一个BCD(二进制编码的十进制)数加法器,名为bcd_fadd,它将两个BCD数字和进位信号相加,生成结果和进位信号。

1

2

3

4

5

6

| module bcd_fadd {

input [3:0] a,

input [3:0] b,

input cin,

output cout,

output [3:0] sum );

|

实例化bcd_fadd的4个副本,以创建一个4位BCD行波进位加法器。

Solution4:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

| module top_module(

input [15:0] a, b,

input cin,

output cout,

output [15:0] sum );

wire [2:0] cout_temp;

bcd_fadd bcd_1(a[3:0],b[3:0],cin,cout_temp[0],sum[3:0]);

bcd_fadd bcd_2(a[7:4],b[7:4],cout_temp[0],cout_temp[1],sum[7:4]);

bcd_fadd bcd_3(a[11:8],b[11:8],cout_temp[1],cout_temp[2],sum[11:8]);

bcd_fadd bcd_4(a[15:12],b[15:12],cout_temp[2],cout,sum[15:12]);

endmodule

|

总结

- 学习了常见加法器的原理与设计

- 学习了带进位加法器的级联