HDLBits答案(15)_Verilog有限状态机(2)

Verilog有限状态机(2)

前言

继续更新状态机小节的习题。

题库

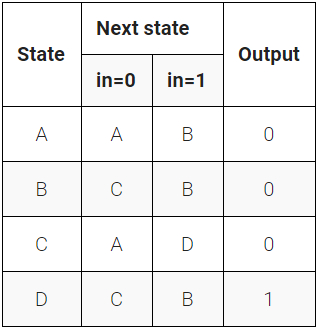

题目描述6:

Solution6:

1 | module top_module( |

本题中作者想让我们以one-hot(独热码)的编码逻辑来完成。一般状态机为了方便编码都是设置为二进制;但若状态转移是按顺序进行转移的话,我们可以使用格雷码,因为两相邻状态之间只变化1bit,这样可以节约功耗;若想提升速度,可以使用one-hot编码,因为每次仅需判断一位,这是用寄存器资源换组合逻辑资源,以达到更高的速度。

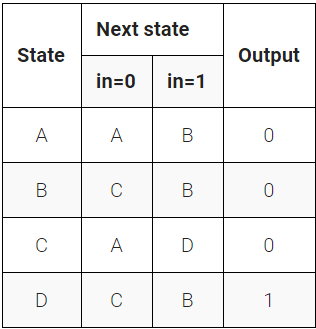

题目描述7:

题目与上题相同,区别为异步复位,复位至状态A。

Solution7:

1 | module top_module( |

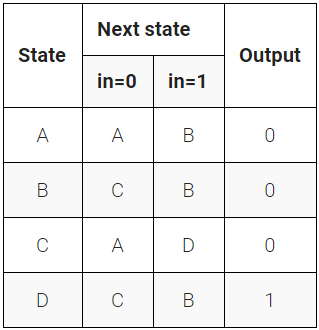

题目描述8:

题目同上题,将复位改为同步复位。

Solution8:

1 | module top_module( |

题目描述9:

Solution9:

1 | module top_module ( |

小结

今天先更新这几道题目,重点是one-hot编码部分,了解其与格雷码的优缺点。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 大卫的博客园!

评论