Verilog移位寄存器

HDLBits链接

前言

今天更新一节内容,该小节题目不多,共三道,但技巧性挺强。

题库

题目描述1:各单元的下一状态是此时当前单元相邻两位的异或。

在这个电路中,创建一个512单元系统(q(511:0)),并在每个时钟周期中前进一个时间步长。加载(load)表明系统的状态应该加载data[511:0]至q中,假设边界(q[0]和q[512])都为零。

Solution1:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

| module top_module(

input clk,

input load,

input [511:0] data,

output [511:0] q );

always @(posedge clk)begin

if(load)begin

q <= data;

end

else begin

q <= {1'b0,q[511:1]}^{q[510:0],1'b0};

end

end

endmodule

|

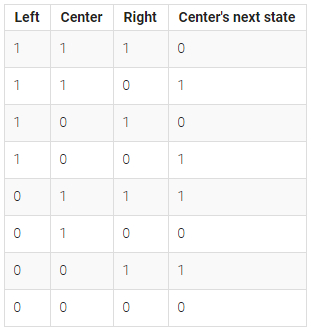

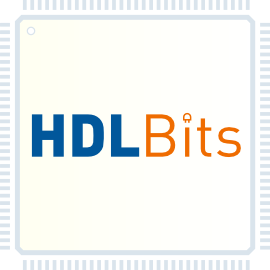

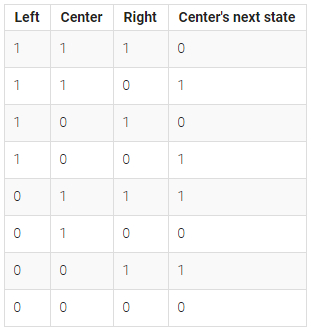

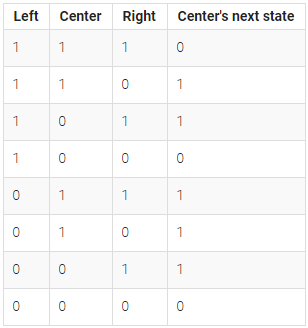

题目描述2:

与题目一类似,状态转移条件发生变化,如下图所示:

Solution2:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

| module top_module(

input clk,

input load,

input [511:0] data,

output [511:0] q

);

always @(posedge clk)begin

if(load)begin

q <= data;

end

else begin

q <= (~{1'b0,q[511:1]} & q) | (q & ~{q[510:0],1'b0}) | {~{1'b0,q[511:1]} & {q[510:0],1'b0}} | {~q & {q[510:0],1'b0}};

end

end

endmodule

|

tips:进行卡诺图化简后可看懂q状态转移的含义。

题目描述3:

一个中心点周围有8个邻居,如果周围的邻居中1的数目为0-1个,那么中心点变为0;如果周围邻居中1的数目为2个,那么中心点状态不变;如果周围邻居中1的数目为3个,中心点变为1;如果周围邻居中1的数目大于3个,中心点变为0。

我们可以将周围的8个邻居的值都加起来来判断周围邻居中1的个数,值得注意的是,这里我们在for中使用了阻塞赋值,因需要当前拍(本周期)得到结果在当前拍(本周期)就去判断。

建议大家做该题的时候花一个16*16的方阵,分析边界条件,达到事半功倍的效果。

生命游戏之父约翰·康威因感染新冠于2020年4月11日去世,享年83岁,在此表示哀悼。

Solution3:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

| module top_module(

input clk,

input load,

input [255:0] data,

output [255:0] q );

reg [3:0] count[255:0];

integer i;

always @(*) begin

for(i=0;i<256;i++)begin

if(i == 0)begin

count[i] = q[255] + q[240] + q[241] + q[15] + q[1] + q[31] + q[16] + q[17];

end

else if(i == 15)begin

count[i] = q[254] + q[255] + q[240] + q[14] + q[0] + q[30] + q[31] + q[16];

end

else if(i == 240)begin

count[i] = q[239] + q[224] + q[225] + q[255] + q[241] + q[15] + q[0] + q[1];

end

else if(i == 255)begin

count[i] = q[238] + q[239] + q[224] + q[254] + q[240] + q[15] + q[0] + q[14];

end

else if( i>0 && i<15)begin

count[i] = q[239+i]+q[240+i]+q[241+i]+q[i-1]+q[i+1]+q[i+15]+q[i+16]+q[i+17];

end

else if(i>240 && i<255)begin

count[i] = q[i-17]+q[i-16]+q[i-15]+q[i-1]+q[i+1]+q[i-239]+q[i-240]+q[i-241];

end

else if( i%16 == 0)begin

count[i] = q[i-1]+q[i-16]+q[i-15]+q[i+15]+q[i+1]+q[i+31]+q[i+16]+q[i+17];

end

else if(i % 16 == 15)begin

count[i] = q[i-17]+q[i-16]+q[i-31]+q[i-1]+q[i-15]+q[i+15]+q[i+16]+q[i+1];

end

else begin

count[i] = q[i-17]+q[i-16]+q[i-15]+q[i-1]+q[i+1]+q[i+15]+q[i+16]+q[i+17];

end

end

end

always @(posedge clk)begin

if(load)begin

q <= data;

end

else begin

for(i=0;i<256;i++)begin

case(count[i])

4'd2:q[i] <= q[i];

4'd3:q[i] <= 1'b1;

default:q[i] <= 1'b0;

endcase

end

end

end

endmodule

|

小结

希望自己以后遇到问题能够慢慢划分解决,徐图缓进。