HDLBits答案(1)_Verilog语法基础

HDLBits_Verilog语法基础

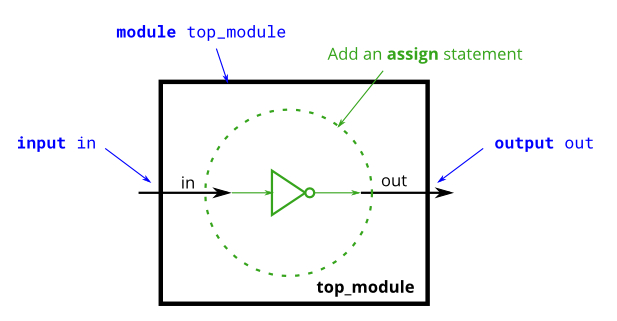

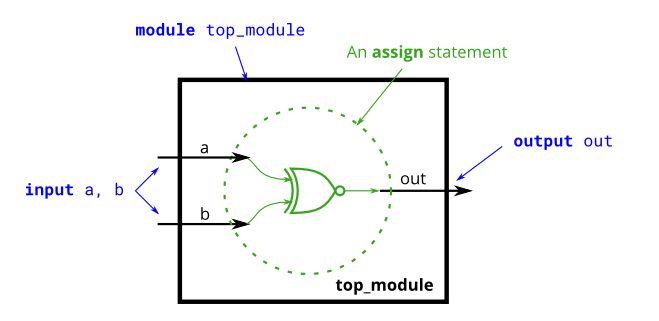

线信号

与物理电线不同,Verilog中的线信号(和其他信号)是“方向性的”。这意味着信息只向一个方向流动,从驱动程序流向接收器。在Verilog“连续赋值”(assign left_side = right_side;)中,右侧信号的值被驱动到左侧的连接上。assign赋值是“连续的”,右侧的值发生变化时左边的值立马发生变化。

这时我们就会理解:一个线信号不能有两个驱动程序来驱动;线信号如果没有驱动程序的话那么输出就是未知的。

当存在多个assign语句时,assign出现的顺序和位置不影响,也就相当于连线的顺序不影响最终结果,这个要和软件的思维区别开。

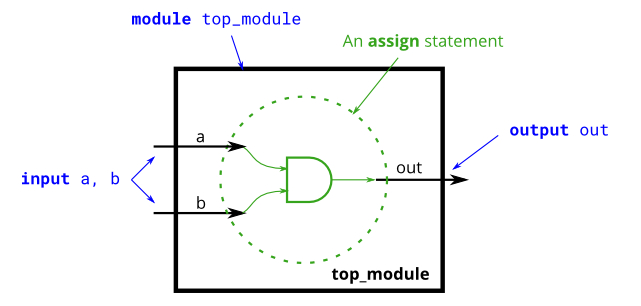

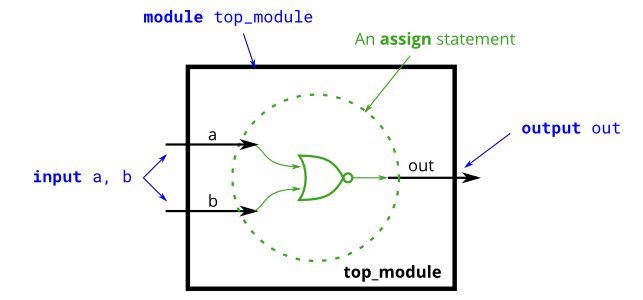

基础的门操作

区分按位取反(~) 和逻辑取反(!)

区分按位与(&)和逻辑与(&&)

区分按位或(|)和逻辑或(||)

A NOR gate is an OR gate with its output inverted.

按位异或

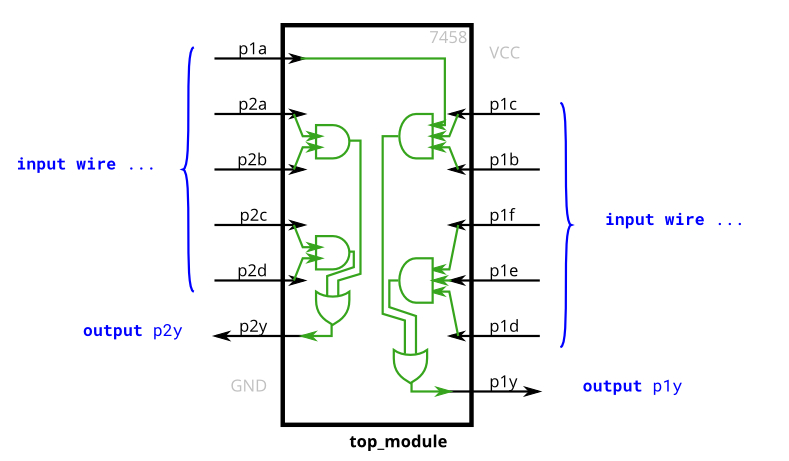

7458芯片

题目描述:

按照电路图,用verilog语言描述输入输出间的关系。

Solution1:

1 | module top_module ( |

Soluton2:

1 | module top_module ( |

总结

1、assign为连续赋值,赋值顺序不影响。

2、一个wire有且仅能有一个driver。

3、学习了基础的门操作。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 大卫的博客园!

评论